# Leonardo Haas Peçanha Lessa

Desenvolvimento da unidade de controle do módulo de aquisição de dados para o upgrade do experimento LHCb

# Leonardo Haas Peçanha Lessa

Desenvolvimento da unidade de controle do módulo de aquisição de dados para o upgrade do experimento LHCb

Dissertação apresentada à Coordenação de Formação Cientifica do Centro Brasileiro de Pesquisas Físicas para a obtenção do titulo de Mestre em Física com ênfase em Instrumentação Cientifica.

Orientador: André Massafferri Rodrigues

Ministério da Ciência, Tecnologia e Inovação Centro Brasileiro de Pesquisas Físicas Mestrado Profissional Em Física

Rio de Janeiro - RJ

Agosto / 2013

# Agradecimentos

Em primeiro lugar, agradeço aos meus pais e minha irmã, por todo o carinho, suporte e educação, dado em toda minha vida.

À minha esposa Cristina, que não me deixou desistir em momento algum do objetivo através de suas palavras de incentivo. Mesmo com minha ausência constante após o primeiro mês do nascimento do nosso filho Eric.

Ao meu orientador André Massafferri por todo suporte oferecido para a realização deste trabalho, pela grande compreensão e todo esforço feito para me manter no CERN. Além é claro do incentivo final para o término trabalho.

Ao pesquisador Ignácio Bediaga pelo apoio e colaboração no financiamento do projeto.

Ao pesquisador Alexandre Mello, pela compreensão relativa ao atraso para a apresentação desta dissertação.

Ao Niko Neufeld e Beat Jost do grupo *Online* do LHCb por me inserirem no grupo do CERN e pelo material fornecido para o desenvolvimento deste trabalho.

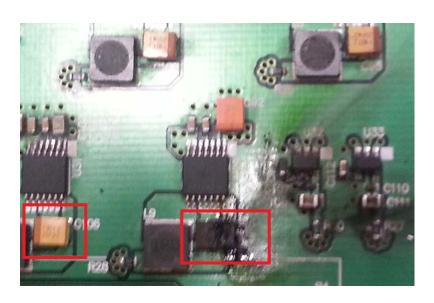

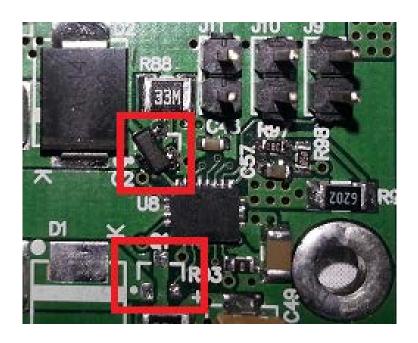

Ao colega de profissão e amigo, Diogo Di Calafiori, por disponibilizar o laboratório para os testes dos protótipos, sugestões e ideias e principalmente pela enorme paciência no trabalho de conserto das placas, incluindo a solda em componentes que dificilmente se enxergava.

Aos amigos brasileiros do CERN, pelos almoços, conversas e momentos de diversão vividos.

E finalmente aos familiares e amigos presentes em minha vida e que, de maneira direta ou indireta, me apoiaram e incentivaram para que seguisse em frente.

## Resumo

O presente documento descreve o desenvolvimento do módulo de sistema de controle e suas camadas de software para o upgrade do sistema de aquisição de dados previsto no experimento LHCb. Este módulo é capaz de realizar o controle de uma placa de aquisição assim como outros dispositivos situados em áreas livres de radiação, de forma centralizada com a intermediação de um computador embarcado no módulo e o uso da comunicação Gigabit Ethernet através de barramentos de baixa velocidade como, I²C e JTAG assim como a comunicação em alta velocidade utilizando o protocolo PCI Express. Também é descrito o desenvolvimento de uma placa de validação do módulo para uso na verificação do protótipo, particularmente importante para a produção em série. Serão apresentados os resultados obtidos através do uso de um kit de desenvolvimento, por consequência da impossibilidade da utilização do primeiro protótipo do módulo, com destaque a simplicidade de operação de dispositivos I²C através do sistema operacional e desempenho na comunicação em alta velocidade.

## **Abstract**

This document describes the development of the control system module and related software layers focused to the DAQ system upgrade of the LHCb experiment. This module is able to control a DAQ board as well as other generic devices located in radiation free areas. It can be managed centrally through an embedded computer module, using the Gigabit Ethernet communication to control, monitoring and configuring low-speed buses such as, I²C and JTAG as well as high speed communication PCI Express protocol. It also describes the development of a validation board to be used to test the prototype and particularly important for mass production period. It is presented the results extracted using a development kit, since first prototype of the module was not properly working. We highlight the simplicity of operation I²C devices through the operating system and performance in high-speed communication.

# Sumário

| Lis | ta de                                  | e Figu | ras                                               | vi     |

|-----|----------------------------------------|--------|---------------------------------------------------|--------|

| Lis | ta de                                  | e Tabe | elas                                              | . viii |

| Lis | ta de                                  | e abre | viaturas e siglas                                 | ix     |

| 1.  | Int                                    | trodu  | ção                                               | 1      |

| 2.  | Ac                                     | elera  | dor LHC                                           | 5      |

| 3.  | 3. LHCb (Large Hadron Collider Beauty) |        |                                                   | 8      |

|     | 3.1                                    | Ma     | gneto                                             | 9      |

|     | 3.2                                    | Sist   | tema de traços                                    | 9      |

|     | 3.2                                    | 2.1    | VELO                                              | . 10   |

|     | 3.2                                    | 2.2    | Silicon Tracker                                   | . 10   |

|     | 3.2                                    | 2.3    | Outer Tracker                                     | . 11   |

|     | 3.3                                    | RIC    | `H                                                | . 11   |

|     | 3.4                                    | Cal    | orímetros                                         | . 12   |

|     | 3.5                                    | Sist   | tema de Múons                                     | . 13   |

|     | 3.6                                    | Sist   | tema de trigger                                   | . 14   |

|     | 3.7                                    | Sist   | tema Online                                       | . 15   |

| 4.  | Up                                     | ograde | e da eletrônica e sistema online do LHCb          | . 22   |

|     | 4.1                                    | Ele    | trônica de <i>Front-end</i>                       | . 24   |

|     | 4.2                                    | Arc    | quitetura geral da interface TFC/ECS no Front-end | . 25   |

|     | 4.3                                    | Pla    | cas de <i>readout</i>                             | . 26   |

|     | 4.3                                    | 3.1    | ECS nas placas de readout                         | . 29   |

|     | 4.4                                    | Arc    | quitetura de <i>readout</i>                       | . 29   |

| 5.  | 0                                      | Módu   | lo ECS-CBPF                                       | . 36   |

|     | 5.1                                    | Pro    | otocolos e barramentos de comunicação             | . 38   |

|     | 5.3                                    | 1.1    | Barramento PCIe                                   | . 38   |

|     | 5.2                                    | 1.2    | Barramento I <sup>2</sup> C                       | . 39   |

|     | 5.3                                    | 1.3    | JTAG                                              | . 41   |

|     | 5.2                                    | Fer    | ramentas de desenvolvimento                       | . 42   |

| 5     | .3                              | Kit de desenvolvimento Cyclone IV (DB4  | CGX15) 43                               |

|-------|---------------------------------|-----------------------------------------|-----------------------------------------|

| 5     | 5.4 Desenvolvimento do Hardware |                                         | 44                                      |

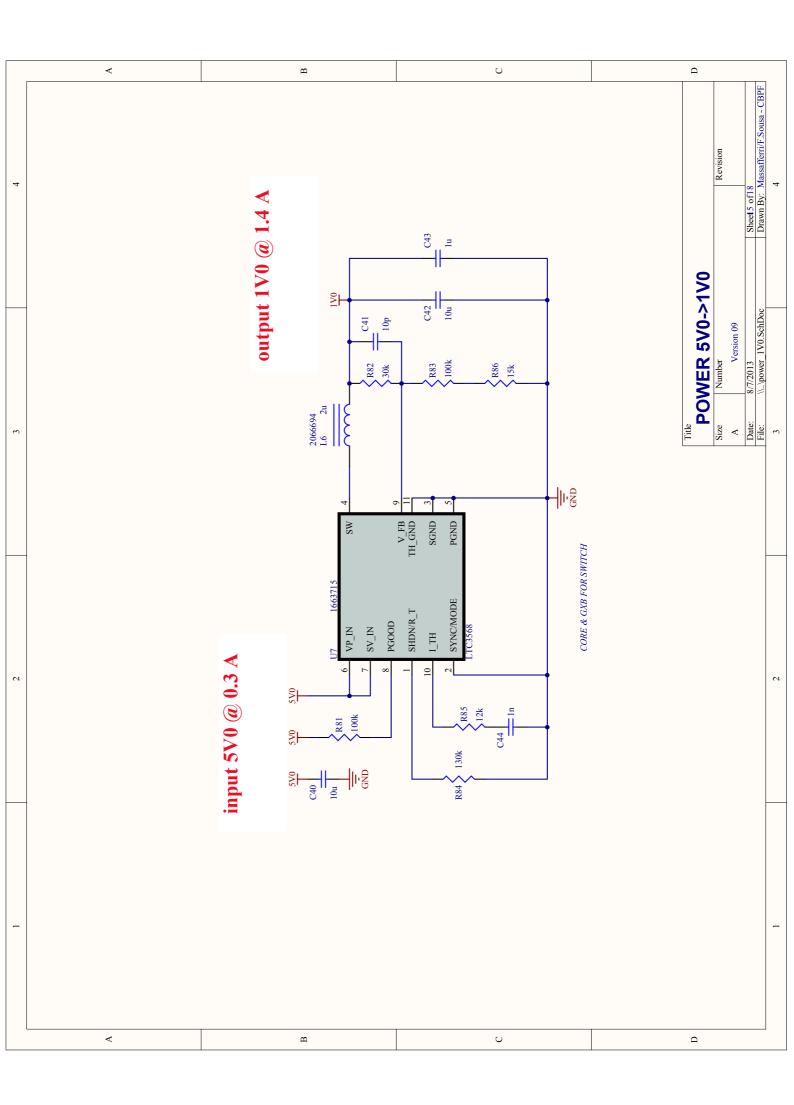

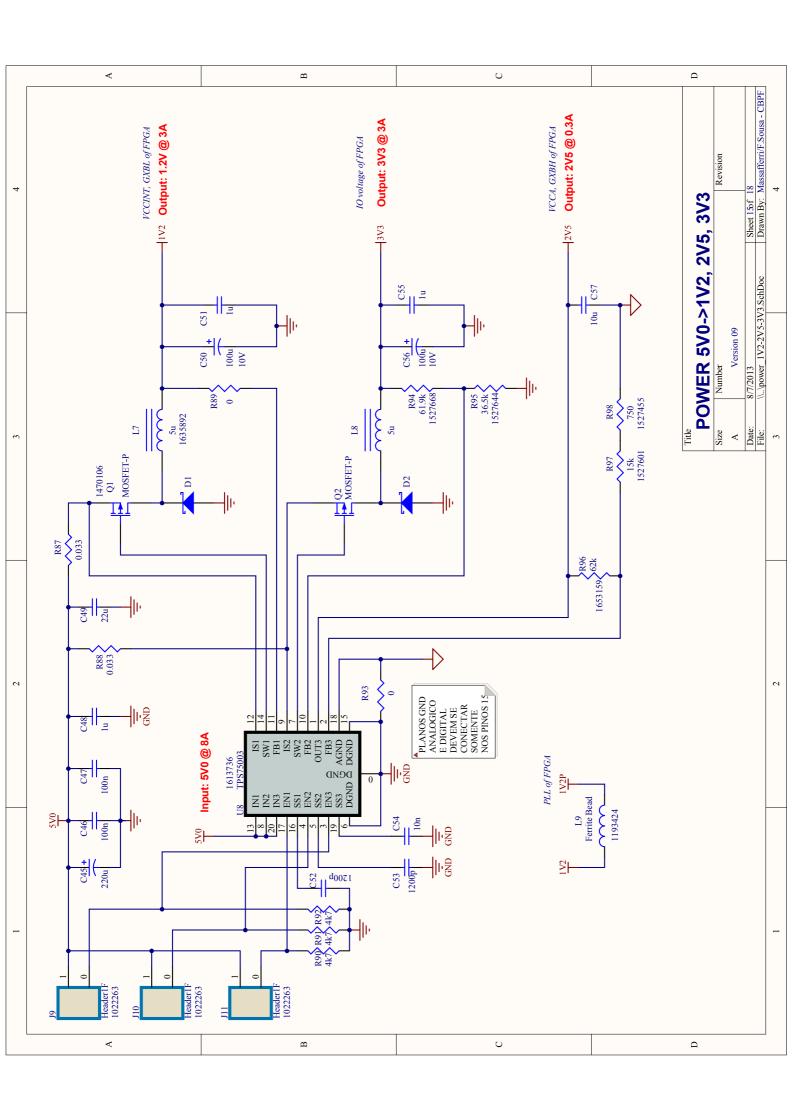

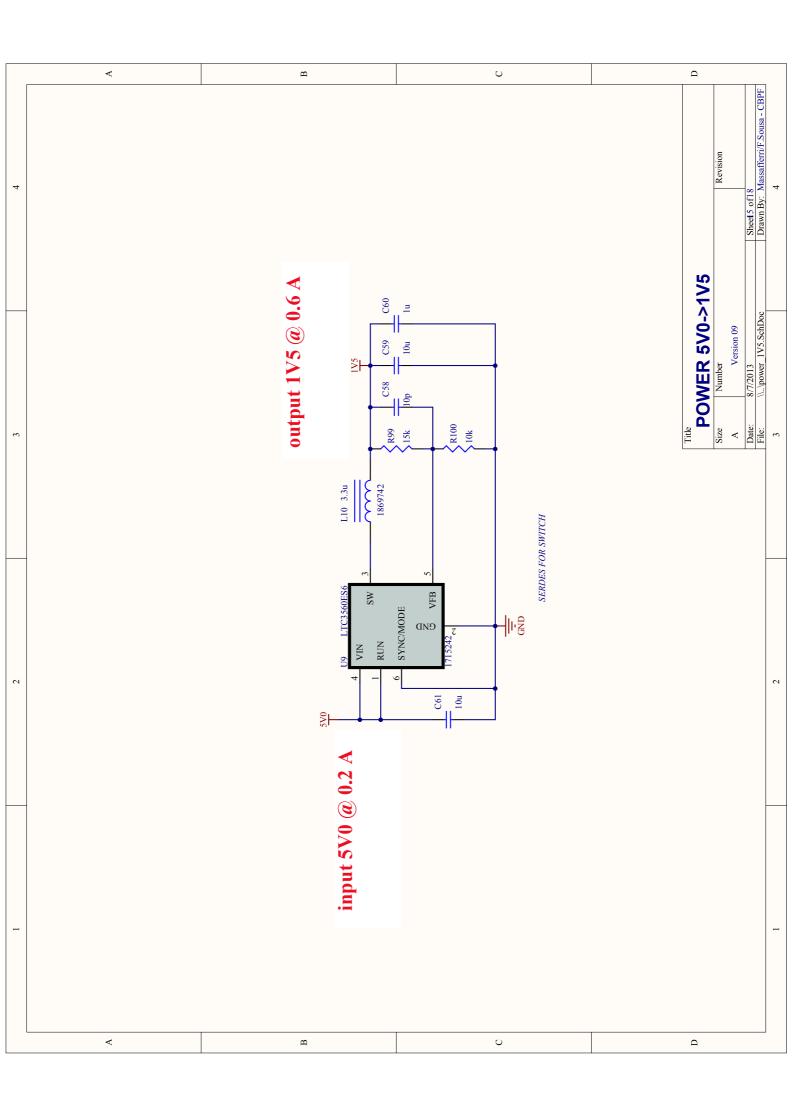

| 5.4.1 |                                 | 1 Distribuição de alimentação           | 44                                      |

| 5.4.2 |                                 | 2 Distribuição de Clock                 | 44                                      |

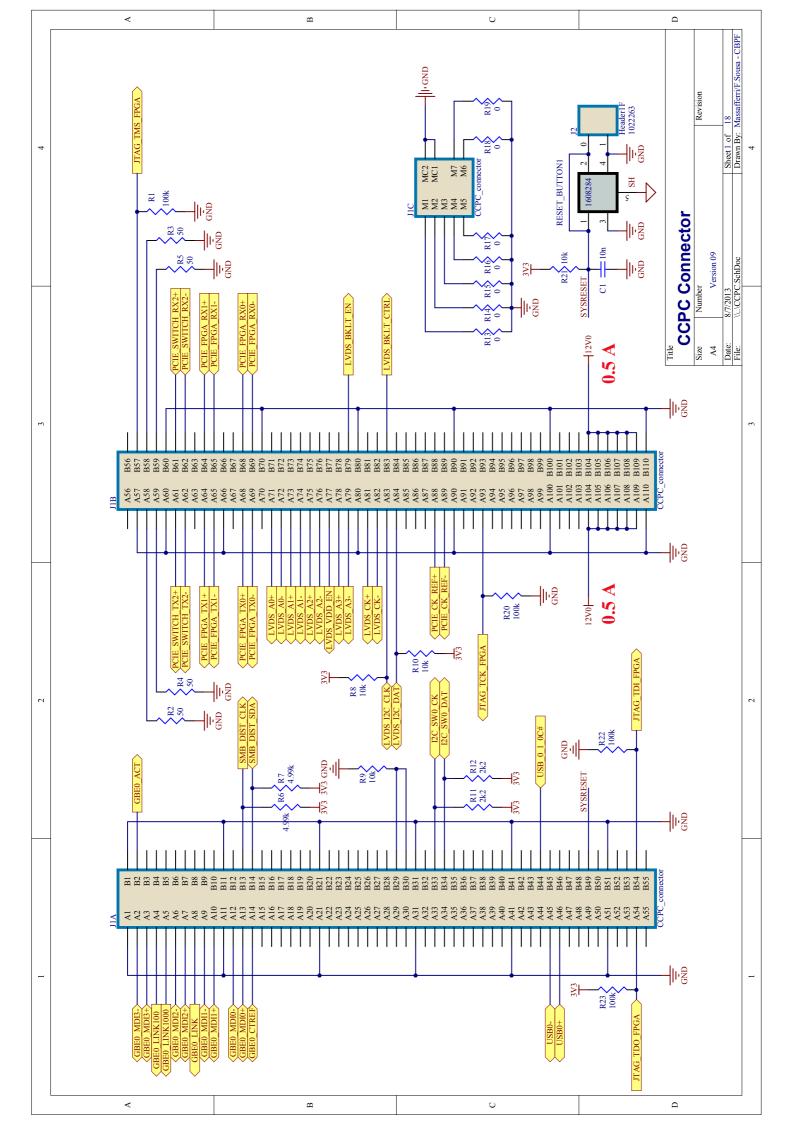

|       | 5.4.3                           | 3 CCPC                                  | 45                                      |

|       | 5.4.                            | 4 Switch PCIe                           | 46                                      |

|       | 5.4.                            | 5 FPGA                                  | 47                                      |

| 5     | .5                              | Desenvolvimento do Firmware             | 47                                      |

|       | 5.5.                            | 1 O SOPC Builder                        | 48                                      |

| 5     | .6                              | Desenvolvimento de Software             | 52                                      |

|       | 5.6.                            | 1 Sistema Operacional                   | 52                                      |

|       | 5.6.                            | 2 ECS-CBPF Drivers                      | 56                                      |

|       | 5.6.3                           | 3 Programas e bibliotecas               | 62                                      |

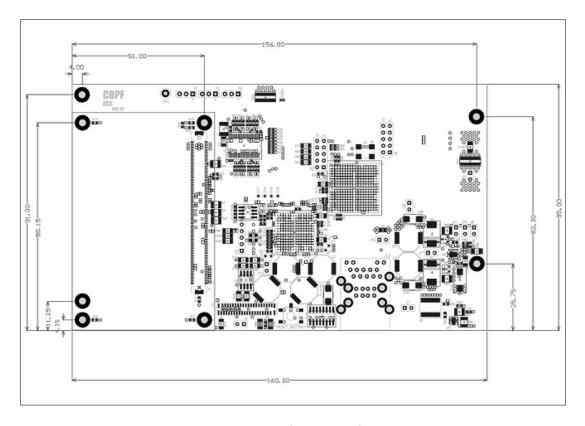

| 5     | .7                              | Geometria e Interconexões               | 63                                      |

|       | 5.7.                            | 1 Geometria                             | 63                                      |

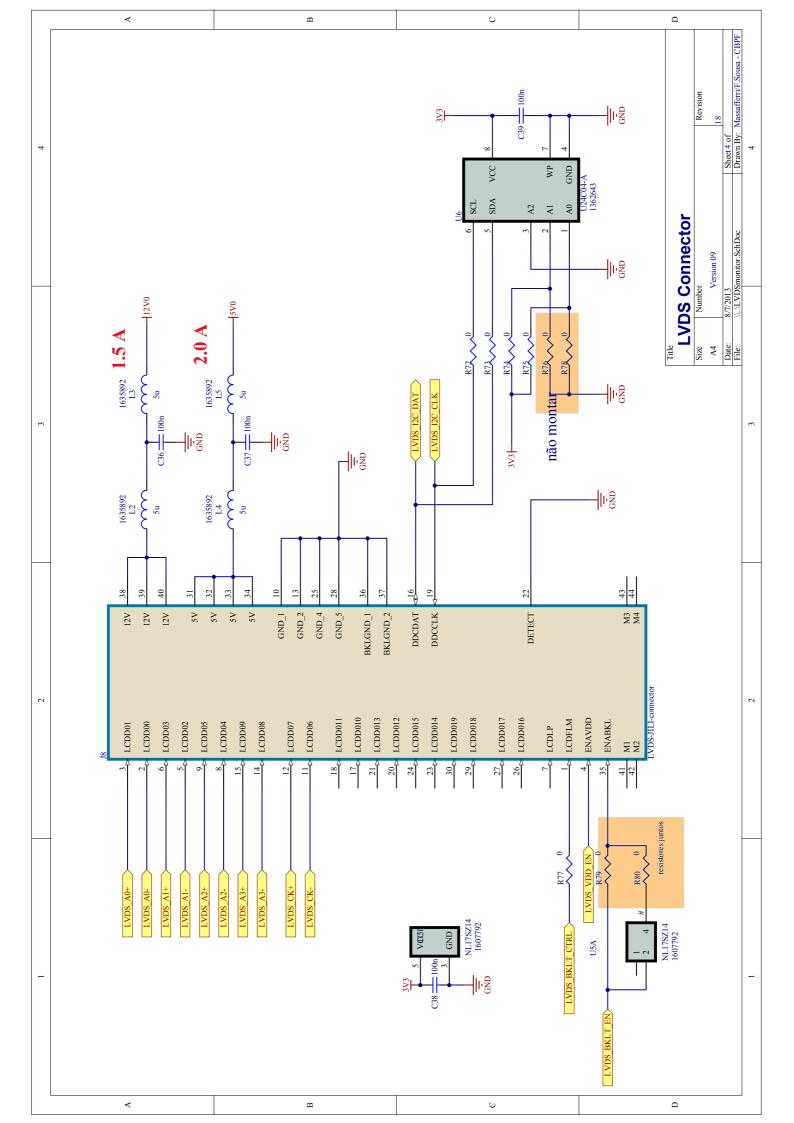

|       | 5.7.                            | 2 Conector LVDS (Vídeo)                 | 64                                      |

|       | 5.7.                            | 3 RJ45 e USB                            | 64                                      |

|       | 5.7.                            | 4 Conector JTAG                         | 64                                      |

|       | 5.7.                            | 5 Conector Samtec                       | 64                                      |

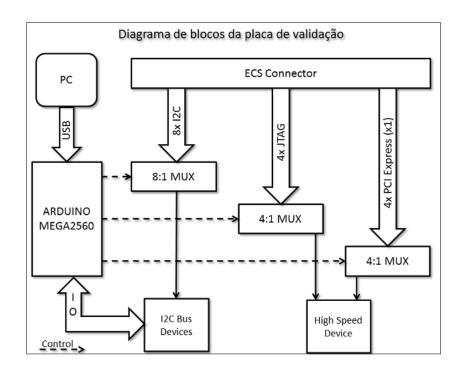

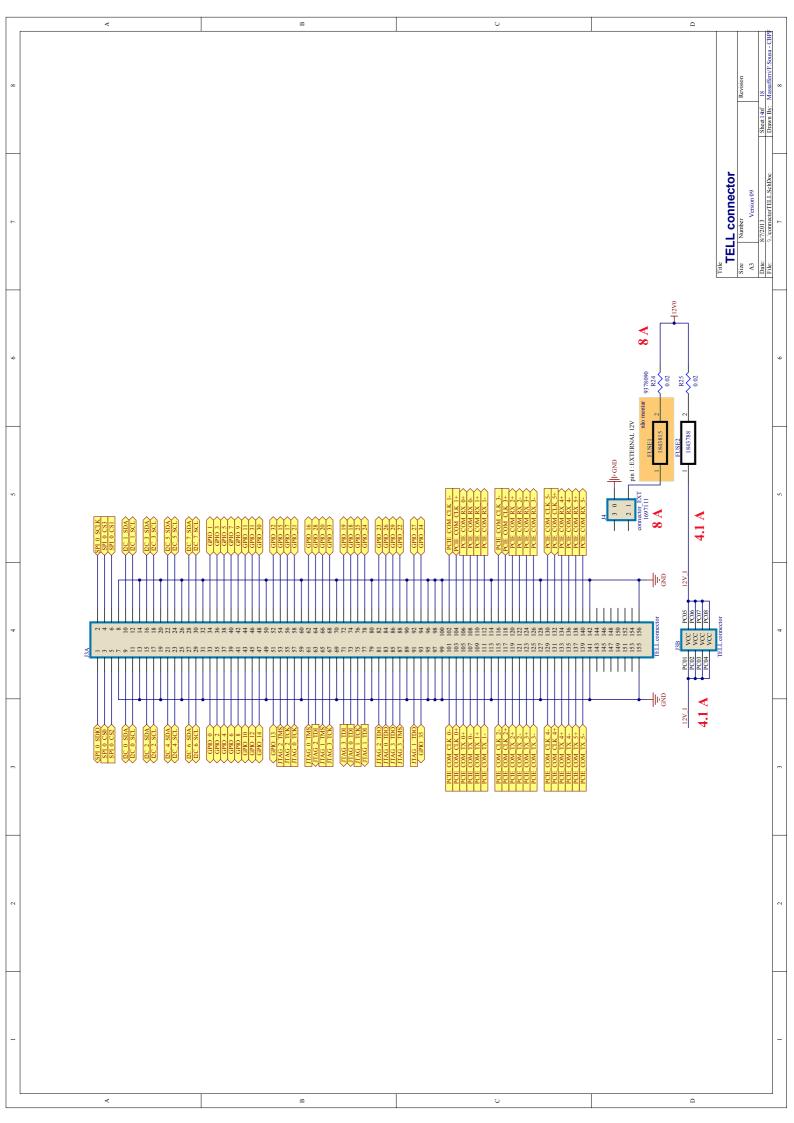

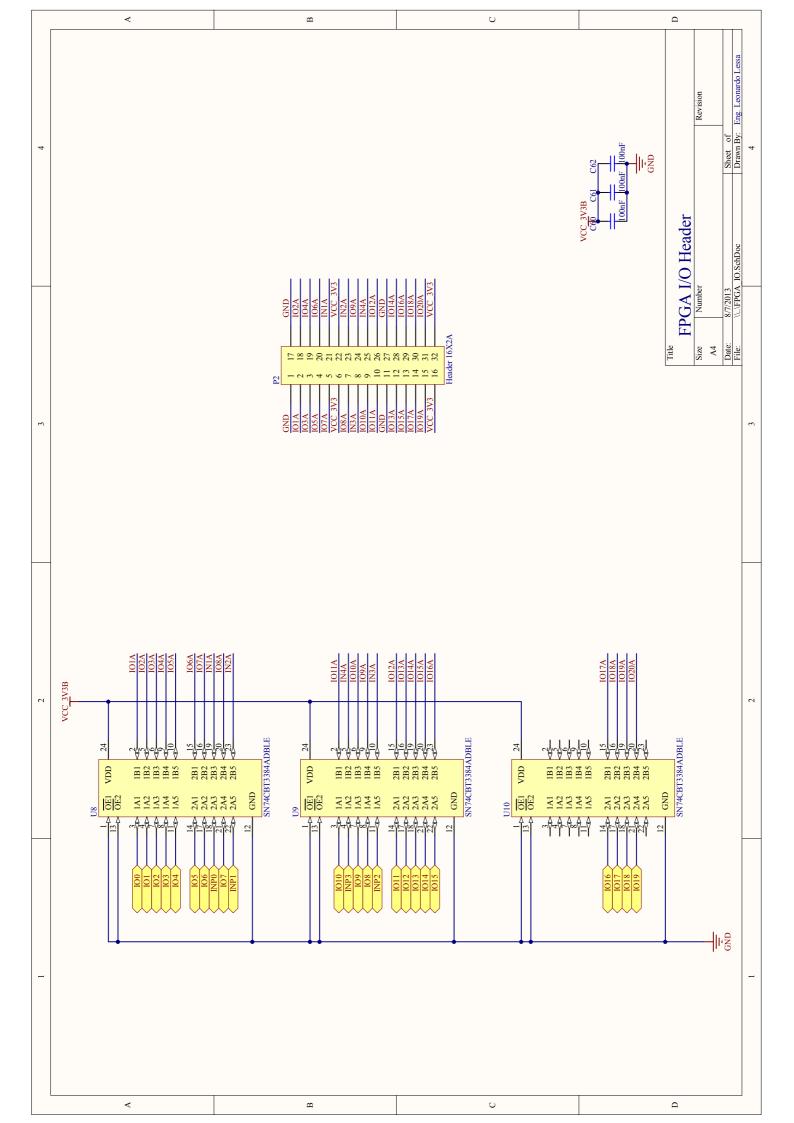

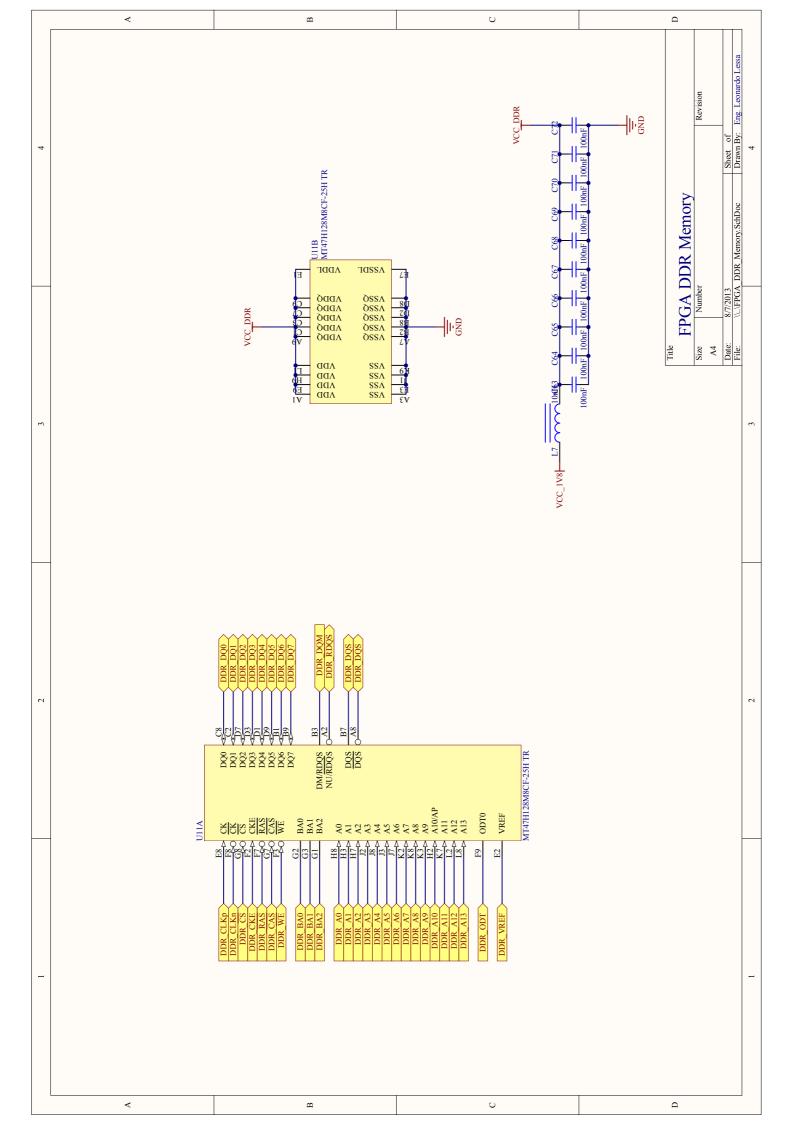

| 6.    | Plac                            | ca de validação do módulo ECS-CBPF      | 65                                      |

| 6     | 5.1                             | Desenvolvimento do Hardware             | 66                                      |

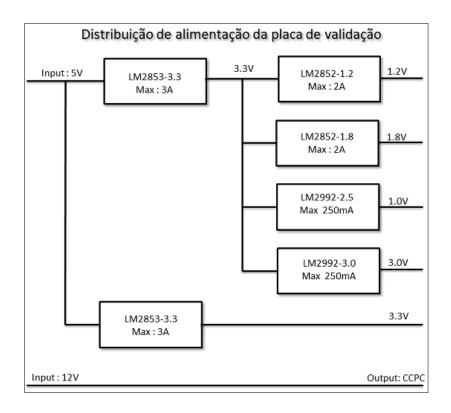

|       | 6.1.                            | 1 Distribuição de alimentação           | 66                                      |

|       | 6.1.                            | 2 Módulo de controle de teste           | 67                                      |

|       | 6.1.3                           | 3 Dispositivos I <sup>2</sup> C         | 68                                      |

|       | 6.1.                            | 4 Dispositivo para teste de configura   | ção e comunicação em alta velocidade 69 |

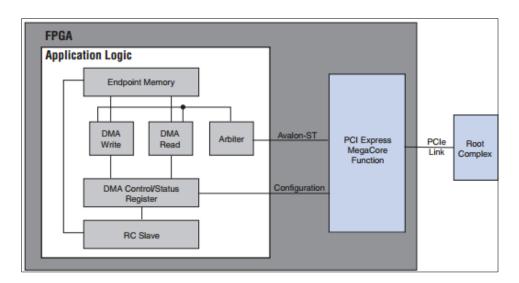

| 6     | 5.2                             | Desenvolvimento do Firmware             | 69                                      |

| 6     | 5.3                             | Desenvolvimento do driver               | 72                                      |

| 7.    | Resu                            | ultados                                 | 73                                      |

| 7     | '.1                             | Verificação dos protótipos              | 73                                      |

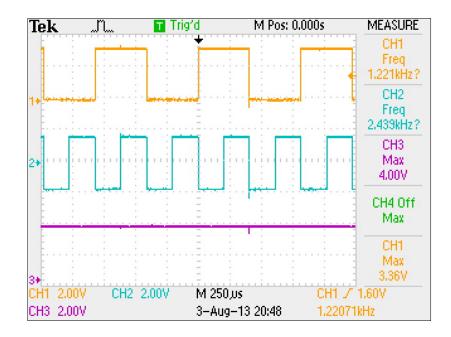

| 7     | .2                              | Verificação do protocolo I2C            | 73                                      |

| 7     | .3                              | Verificação da interface JTAG           | 76                                      |

| 7     | .4                              | Verificação de transmissão em alta velo | cidade PCIe79                           |

| 8.    | Con                             | clusão e perspectivas futuras           |                                         |

| Ref   | Referências Bibliográficas      |                                         |                                         |

|       |                                 |                                         |                                         |

# Lista de Figuras

| FIGURA 1 - TUNEL DO LHC                                       | 5    |

|---------------------------------------------------------------|------|

| FIGURA 2 - PRÉ-ACELERADORES                                   | 6    |

| FIGURA 3 - DETECTOR LHCB                                      | 8    |

| FIGURA 4 – MAGNETO                                            | 9    |

| FIGURA 5 - SUB-DETECTOR VELO                                  | 10   |

| FIGURA 6 - SUB-DETECTOR RICH                                  |      |

| FIGURA 7 - GRANULARIDADE DOS CALORÍMETROS                     |      |

| FIGURA 8 - SISTEMA DE MÚONS                                   |      |

| FIGURA 9 - SISTEMA <i>ONLINE</i>                              |      |

| FIGURA 10 - DIAGRAMA DE BLOCOS SIMPLIFICADO DA TELL1          |      |

| FIGURA 11 – ARQUITETURA DO SISTEMA TFC                        |      |

| FIGURA 12 - SISTEMA HIERÁRQUICO E DISTRIBUÍDO                 |      |

| FIGURA 13 - ARQUITETURA GERAL DO UPGRADE NA ELETRÔNICA        |      |

| FIGURA 14 - TÍPICO MÓDULO DE FE                               |      |

| FIGURA 15 - PLACA ATCA COM QUATRO MÓDULOS AMC                 |      |

| FIGURA 16 - ARQUITETURA DA PLACA AMC40                        | 27   |

| FIGURA 17 - PLACA ATCA40                                      |      |

| FIGURA 18 - ARQUITETURA DE READOUT COM SWITCH EXTERNO         |      |

| FIGURA 19 - CONFIGURAÇÃO TELL40                               |      |

| FIGURA 20 - CONFIGURAÇÃO FSC40                                |      |

| FIGURA 21 - CONFIGURAÇÃO ODIN40                               |      |

| FIGURA 22 - CONFIGURAÇÃO TFCI40                               |      |

| FIGURA 23 - CONFIGURAÇÃO TRIG40                               | 35   |

| FIGURA 24 - MÓDULO EXPERIMENT CONTROL SYSTEM – CCPC CBPF      |      |

| FIGURA 25 - DIAGRAMA DE BLOCOS DO MÓDULO ECS-CBPF             |      |

| FIGURA 26 - PACOTE DE DADOS PCIE                              |      |

| FIGURA 27 - BARRAMENTO I <sup>2</sup> C                       |      |

| FIGURA 28 - PROTOCOLO I <sup>2</sup> C                        |      |

| FIGURA 29 - MÁQUINA DE ESTADO DO CONTROLADOR JTAG             |      |

| FIGURA 30 - CONFIGURAÇÃO DE UMA CHAIN JTAG                    | 42   |

| FIGURA 31 - KIT DE DESENVOLVIMENTO DB4CGX15                   |      |

| FIGURA 32 - DISTRIBUIÇÃO DA ALIMENTAÇÃO DO MÓDULO ECS         |      |

| FIGURA 33 - DISTRIBUIÇÃO DE CLOCK DE REFERÊNCIA PCIE          |      |

| FIGURA 34 - MÓDULO CCPC KONTRON                               |      |

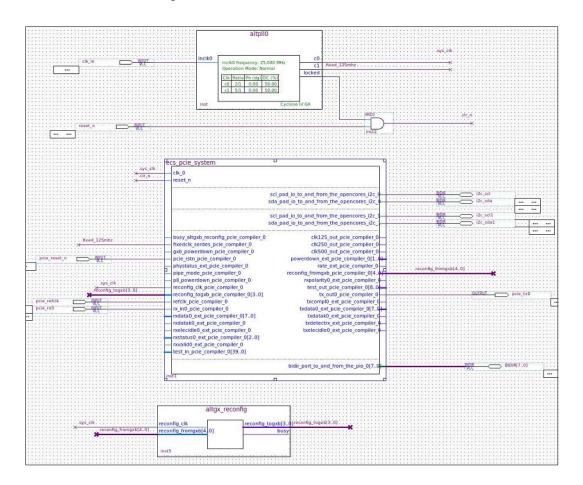

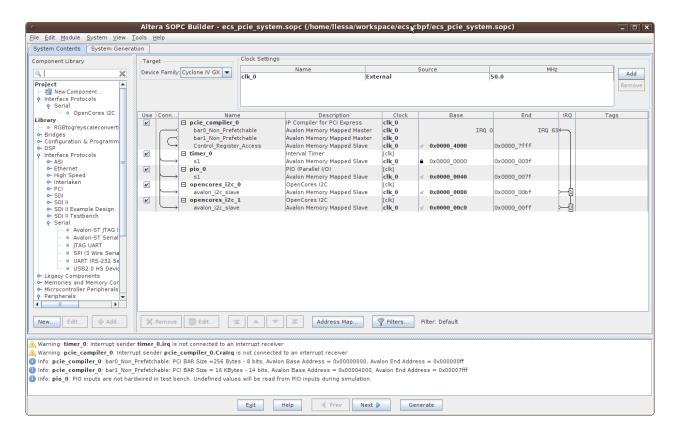

| FIGURA 35 - TELA DO PROJETO ECS-CBPF EM AMBIENTE GRÁFICO      |      |

| FIGURA 36 - TELA DE INTEGRAÇÃO ENTRE DISPOSITIVOS NO SOPC     |      |

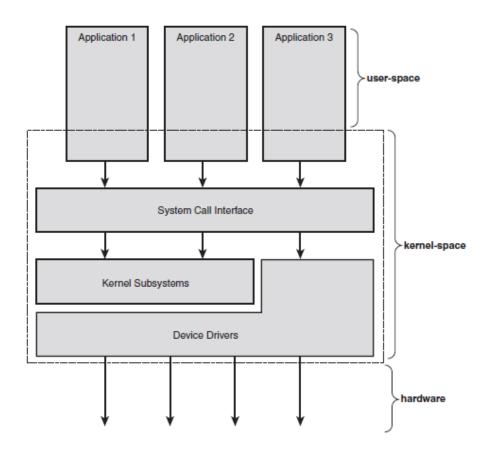

| FIGURA 37 - RELAÇÃO ENTRE APLICAÇÕES, KERNEL E HARDWARE       |      |

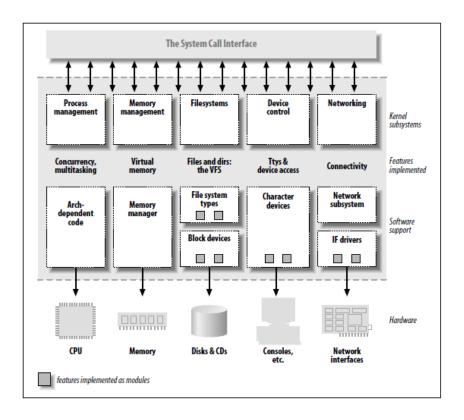

| FIGURA 38 - DIAGRAMA DAS DIVISÕES DOS MÓDULOS NO KERNEL       |      |

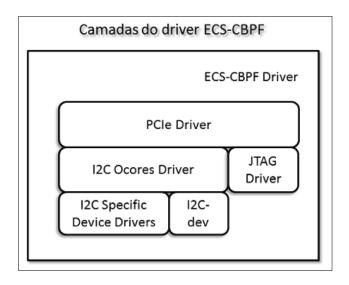

| FIGURA 39 - CAMADAS DO DRIVER ECS-CBPF                        |      |

| FIGURA 40 - CAMADAS DO SUBSISTEMA I <sup>2</sup> C            |      |

| FIGURA 41 - ESQUEMA MECÂNICO DO MÓDULO ECS-CBPF               |      |

| FIGURA 42 - DIAGRAMA DE BLOCOS PLACA DE VALIDAÇÃO             |      |

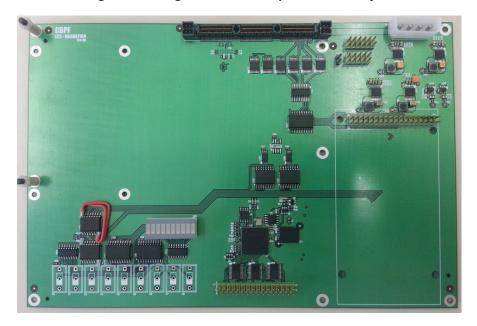

| FIGURA 43 - FOTO DA PLACA DE VALIDAÇÃO                        |      |

| FIGURA 44 - DISTRIBUIÇÃO DE ALIMENTAÇÃO DA PLACA DE VALIDAÇÃO |      |

| FIGURA 45 - DIAGRAMA DE BLOCOS DO FIRMWARE DA PLACA DE VALIDA | ACÃO |

| FIGURA 46 - PROCEDIMENTO DE CARREGAMENTO DOS DRIVERS               | 74 |

|--------------------------------------------------------------------|----|

| FIGURA 47 - PROCEDIMENTO DE CARREGAMENTO DOS DRIVERS               | 75 |

| FIGURA 48 - RESULTADO DO NÍVEL DE TENSÃO NOS REGULADORES           | 75 |

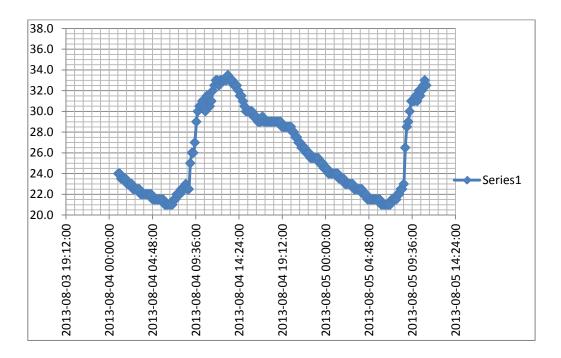

| FIGURA 49 - GRÁFICO DA MEDIDA DE TEMPERATURA AMBIENTE              | 76 |

| FIGURA 50 - PROCESSO DE CARREGA UTILIZANDO A FERRAMENTA JAM PLAYER | 77 |

| FIGURA 51 - CAPTURA DO CÓDIGO EM EXECUÇÃO APÓS O CARREGAMENTO      | 78 |

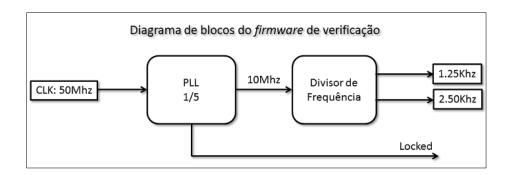

| FIGURA 52 - DIAGRAMA DE BLOCOS DO FIRMWARE DE VERIFICAÇÃO          | 78 |

| FIGURA 53 - UTILIZAÇÃO DA FERRAMENTA URJTAG                        | 79 |

| FIGURA 54 - TRANSFERÊNCIA DE DADOS ENTRE A MEMÓRIA DO PC E FPGA    | 80 |

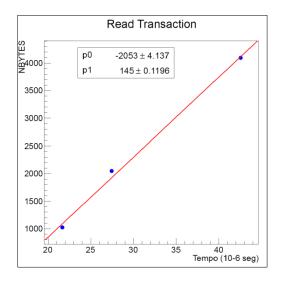

| FIGURA 55 - TRANSAÇÃO DE LEITURA                                   | 83 |

| FIGURA 56 - TRANSAÇÃO DE ESCRITA                                   | 83 |

# Lista de Tabelas

| TABELA 1 - ROTEAMENTO DOS LINKS PCIE                          | 47 |

|---------------------------------------------------------------|----|

| TABELA 2 - BITS DE CONTROLE DOS MULTIPLEXADORES DE BARRAMENTO | 68 |

| TABELA 3 - ENDEREÇOS DO BARRAMENTO I2C                        | 68 |

| TABELA 4 - EFICIÊNCIA E THROUGHPUT                            | 81 |

| TABELA 5 - OPERAÇÃO DE ESCRITA                                | 82 |

| TABELA 6 - OPERAÇÃO DE LEITURA                                | 82 |

|                                                               |    |

## Lista de abreviaturas e siglas

ALICE A Large Ion Collider Experiment

ATLAS A Toroidal LHC ApparatuS

BE Back-End

CAN Controller Area Network CCPC Credit-card sized PC

CERN Centre Européen pour la Recherche Nucléaire CPPM Centre de physique des particules de Marseille

DAQ Data Acquisition System

DLL Data Layer Link

DLLP Data Layer Link Packet

DMA Direct Memory Access

ECAL Electromagnetic Calorimeter

ECS Experiment Control System

EPFL École Polytechnique Fédérale de Lausanne

FE Front-End

FPGA Field-programmable gate array

GBT Gigabit Bidirectional Trigger and Data link

GPIO General Purpose Input/Output

HCAL Hadron Calorimeter

HPD Hybrid Photon Detectors

HLT High Level Trigger

I2C Inter-Integrated Circuit

IT Inner Tracker

JTAG Joint Test Action Group LHC Large Hadron Collider

LHCb Large Hadron Collider beauty

LHCf Large Hadron Collider forward

LLT Large Hadron Collider beauty

MEP Multiple Event Packets

OT Outer tracker

PCIe Peripheral Component Interconnect Express

PL Physical Layer

PS PreShower detector

PSB Proton Syncrotron Booster

RICH Ring Imaging Cherenkov Detector

SCADA Supervisory Control And Data Acquisition

SDP Scintilator Pad Detector

SPECS Serial Protocol for ECS

SPI Serial Peripheral Interface

SPS Super Proton Synchrotron

TFC Trigger and Fast Control

TL Transaction Layer

TLP Transaction Layer Packet

TOTEM TOTal Elastic and diffractive cross section

Measurement

TT Trigger Tracker

TTC Trigger, Timing and Control

VELO Vertex Locator

## 1. Introdução

O experimento LHCb, um dos quatro grandes experimentos situados no acelerador LHC, foi projetado para realizar medidas de precisão envolvendo processos contendo os quarks b (botton) e c (charm), de modo a realizar estudos da violação da simetria CP e procura de Física além do modelo padrão das partículas elementares. Nos últimos anos o experimento vem publicando uma sequência de resultados de excelente qualidade, baseados nos dados acumulados durante os anos 2011 e 2012, o qual totalizou uma luminosidade integrada de 1 e 2 fb-1, respectivamente.

Recentemente a Colaboração LHCb definiu sua estratégia para o upgrade do experimento com o intuito de otimizar a utilização da alta luminosidade que será oferecida pelo acelerador LHC nos próximos anos. O novo regime permitirá o LHCb acumular uma luminosidade integrada de 50 fb-1 num período de 10 anos. A estatística de mésons contendo os *quarks* b e c fornecida proporcionará uma sensibilidade sem precedente à procura de nova Física.

A estratégia definida para o upgrade se divide em duas partes, ambas relacionadas à extinção do *trigger* de nível 0, destinado a reduzir a taxa de eventos a 1 MHz, e a subsequente operação de todos os seus sub-detectores a taxa máxima, correspondente a frequência de colisões do LHC, de 40 MHz. A primeira parte consiste na substituição de alguns detectores de modo a permitir sua utilização em altos regimes de radiação e grandes níveis de ocupação de traços, decorrentes do aumento na luminosidade. A segunda parte se refere unicamente à eletrônica e consiste na adaptação e redesenho da eletrônica de leitura dos detectores (*front-end electronics*) que não operam a 40 MHz, bem como da substituição completa do sistema de aquisição de dados, atualmente baseado em uma placa de aquisição denominada TELL1, por um capaz de processar a formatação de eventos de forma significativamente mais rápida e transmitir dados a uma taxa de 10 Gbs/link. No upgrade será necessária a produção de aproximadamente 300 placas de aquisição com as novas específicações. Estas placas, alocadas em região protegida da radiação (*counting room*), são monitorados e configurados a distância, a partir da sala de controle, parte integrada ao sistema central denominado ECS (*Experiment Control System*). Devido à complexidade de

alguns dispositivos que operam no *counting room* esse controle é desempenhado por unidades locais sofisticadas com a função de estabelecer comunicação em alta velocidade com a sala de controle através do protocolo Ethernet, realizar processamentos locais através de uma pequena CPU (*Credit-Card sized* PC ou CCPC), e ao mesmo tempo permitir a comunicação através de diferentes protocolos como I2C, JTag e SPI. Esses protocolos são utilizados para o controle de parâmetros importantes como temperatura, fluxo de dados, além de permitir o carregamento de firmware de dispositivos FPGAs (*Field-programmable gate array*), comumente encontrados nas placas de aquisição atuais.

No ano de 2009 duas implementações paralelas para o upgrade da placa de aquisição TELL1 estavam sendo estudadas. Uma delas em desenvolvimento pelo mesmo instituto que produziu a TELL1, a EPFL (École polytechnique fédérale de Lausanne), em Lausanne, com o projeto denominado TELL10. A segunda em desenvolvimento pelo CPPM (Centre de physique des particules de Marseille), em Marseille, cujo projeto foi denominado TELL40. Neste período o grupo de eletrônica do CBPF foi convidado a desenvolver a unidade de controle da nova placa de aquisição, para o upgrade do sistema empregado na TELL1, desenvolvido pelo grupo de eletrônica de Genova. O sistema de controle da TELL1 tinha como característica técnica a utilização de um CCPC de 130 MHz, comunicação ethernet de 10/100 Mbs, e o fornecimento de um barramento paralelo, quatro linhas I2C e três interfaces JTAG (Joint Test Action Group). Os pontos críticos no contexto do upgrade do sistema de aquisição consistia na ausência de um protocolo de alta velocidade, como PCIe (Peripheral Component Interconnect Express), no pequeno número de linhas de baixa velocidade, na inexistência do protocolo SPI (Serial Peripheral Interface) e na baixa velocidade da comunicação com a sala de controle, realizada via Ethernet à 100 Mb/s, além da dificuldade da implementação dos drivers de controle e aplicativos para os barramentos de baixa velocidade.

O desenho proposto pelo grupo do CBPF consistiu no desenvolvimento de um *mezzanino*, denominado ECS-CBPF, no qual seria conectado um modelo CCPC do fabricante Kontron com 1GHz de velocidade, e que disponibilizasse Ethernet de 1 Gbs, 6 linhas PCIe e um número configurável de linhas I2C, SPI e JTAG, com controladores implementados dentro de uma FPGA. Expansões seriam possíveis através de portas genéricas (GPIO - *General Purpose Input/Output*), desde que respeitado o limite suportado pela FPGA. Essa dissertação

trata do desenvolvimento de todo o pacote envolvido nesta unidade de controle; *hardware*, *software* e *firmware*. Neste contexto foi produzida também uma placa de validação do módulo ECS-CBPF, importante para o período de produção em série.

Nas várias reuniões que se seguiram, esse desenho se mostrou adequado para as necessidades do upgrade do sistema de controle da TELL1, e genérico suficiente para ser utilizado em outros dispositivos que operem no *counting room*. A geometria proposta inicialmente acompanhava o projeto da TELL10, o qual possuía uma grande modularidade na forma de *mezzaninos*, e, portanto já disponibilizava dimensões específicas.

No ano de 2011 a Colaboração optou pelo projeto da TELL40, uma vez que o grupo de CPPM se encontrava num estágio mais avançado na caraterização dos sinais de alta velocidade. O desenho da placa de aquisição TELL40 previa o desenvolvimento de uma placa mãe a qual serviria de base para quatro mezzaninos denominados AMC40, cada um contendo uma FPGA de altíssimo desempenho. Estas FPGAs desempenham todas as tarefas de formatação de fragmentos dos dados desempenhadas pela TELL40. Segundo o projeto apresentado pela CPPM a placa de aquisição TELL40 seria alocado num crate ATCA, amplamente utilizado na indústria de telecomunicações, considerado como uma concepção mais moderna dos tradicionais crates utilizados em altas energias. Este crate impõe restrições geométricas de modo que foi definido que a implementação do sistema de controle seria na própria placa TELL40, inviabilizando a inserção do mezzanino do CBPF. Porém basicamente todas as funcionalidades de software, principalmente os drivers, e eventualmente algumas firmwares podem ser utilizadas. O projeto do mezzanino ECS-CBPF foi discutido em várias reuniões da Eletrônica e Online do LHCb, onde o andamento do projeto foi apresentado tipicamente de quatro em quatro meses. Uma intensa interação com o grupo de CPPM ainda se verifica no presente momento, principalmente em relação ao suporte de software de baixo nível.

A produção do primeiro protótipo, que inclui o módulo ECS-CBPF e placa de validação, foi dividida em três etapas, produção e fabricação do layout do circuito impresso, e montagem. No momento da verificação foram constatados erros inviabilizaram a obtenção dos resultados. Por este motivo a mesma foi feita através de um kit de desenvolvimento contendo um FPGA similar ao módulo. A partir dos erros detectados na fase de verificação

do primeiro protótipo, um segundo protótipo foi produzido recentemente. Sua verificação esta prevista para o mês de agosto de 2013.

Esta dissertação está dividida em oito capítulos. No capítulo 2 e 3 serão apresentados, respectivamente, o Acelerador LHC com todo o aparato experimental e uma breve descrição do detector LHCb (*Large Hadron Collider beauty*). O capítulo 4 detalha o upgrade previsto para a parte de eletrônica, de *front-end* e aquisição do detector LHCb. O desenvolvimento do módulo ECS-CPBF e placa de validação são tratados respectivamente nos capítulos 5 e 6. Resultados obtidos com a utilização dos elementos criados neste trabalho são encontrados no Capítulo 7 e a conclusão e perspectivas futuras no Capítulo 8.

## 2. Acelerador LHC

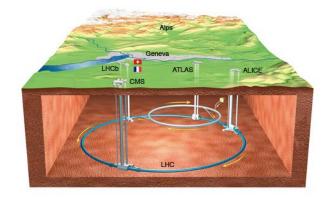

O LHC [1][2](Large Hadron Collider) construído no complexo de pesquisas do CERN (Centre Européen pour la Recherche Nucléaire) está situado na fronteira entre a Suíça e a França. O acelerador encontra-se em um túnel localizado a uma média de 100 m abaixo da superfície, devido a considerações geográficas da região, a profundidade pode variar entre 50 m e 175 m.

Figura 1 - Túnel do LHC

Dentro do acelerador, dois feixes de prótons circulam a uma velocidade próxima a da luz e com uma energia muito alta, antes de colidirem em um dos quatro pontos específicos. Estes feixes trafegam, em direções oposta em anéis separados mantidos em vácuo na ordem de  $10^{-10}$  a  $10^{-11}$  mbar[1] para evitar qualquer interferência de partículas encontradas no ar. Os feixes são guiados ao redor do acelerador por um forte campo magnético através de magnetos supercondutores resfriados a uma temperatura de -271°C. São necessários 1232 dipolos magnéticos que ajudam a manter a direção dos feixes e 392 quadrupolos magnéticos para manter o foco.

Na configuração nominal do LHC, as colisões ocorrem a uma energia de 14 TeV no centro de massa e a uma luminosidade de 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup> em uma frequência de 40MHz.

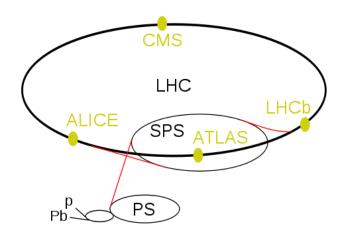

Para atingir a energia nominal os prótons são acelerados por uma série de préaceleradores, como mostrado na Figura 2. Inicialmente os feixes são produzidos a partir da ionização do gás de hidrogênio e passam por um acelerador linear (LINAC2) onde são acelerados até 50 MeV. Em seguida são injetados no PSB (*Proton Syncrotron Booster*) até atingirem a energia de 1.4 GeV. Na etapa seguinte são acelerados pelo PS (*Proton Synchrontron*) até 25 GeV para no SPS (*Super Proton Synchrotron*) atingirem a energia de 450 GeV. Por ultimo, são injetados no LHC em anéis separados que circulam em direções opostas até a energia nominal.

Figura 2 - Pré-Aceleradores

Nos quatro pontos de cruzamento dos feixes existem instalados um total de seis experimentos: ALICE[3] (*A Large Ion Collider Experiment*), ATLAS[4] (*Toroidal LHC ApparatuS*), CMS[5] (*Compact Muon Solenoid*), TOTEM[6] (*TOTal Elastic and diffractive cross section Measurement*), LHCf[7] (*Large Hadron Collider forward*) e o LHCb[8] (*Large Hadron Collider Beauty Experiment*).

O experimento ALICE tem como objetivo estudar através da colisão de ions pesados, a formação do estado da matéria conhecido como plasma de quarks e glúons. Acredita-se que tal plasma tenha existido no Universo, instante após o Big Bang.

O ATLAS e CMS são experimentos de propósito geral, que buscam bóson de Higgs e nova física na escala de TeV.

O experimento TOTEM é dedicado a medidas precisas da seção de choque da interação próton-próton, como também o estudo da estrutura do próton.

O LHCf é um experimento dedicado a medida de partículas neutras emitidas bem próximo a região de colisão. O principal objetivo físico é obter dados para calibração dos modelos de interação de hadrons que são usados no estudo de raios cósmicos de altíssimas energias.

O LHCb tem como principal objetivo estudar o fenômeno de violação de simetria Carga e Paridade (CP) nos decaimentos de sabores pesados, em busca de novos processos físicos, não descritos pelo Modelo Padrão.

# 3. LHCb (Large Hadron Collider Beauty)

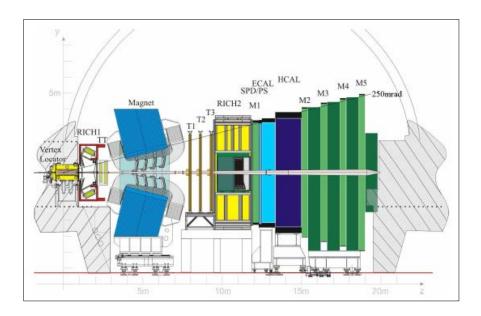

O detector LHCb foi projetado para explorar um grande número de *hadrons*-b produzido no LHC a fim de fazer estudos precisos de assimetrias CP e decaimentos raros no sistema de mésons B. Sua geometria é de um experimento de alvo fixo com uma cobertura angular de 10 mrad a 300 mrad no eixo de projeção horizontal e até 250mrad no eixo de projeção vertical. O layout do detector mostrado na Figura 3 os principais sub-detectores são respectivamente: o detector de vértice (VELO), dois detectores Cherenkov para identificação de partículas (RICH1 e RICH2), um magneto, detectores de trajetórias (TT, T1-T3) e um sistema de calorímetros (SDP, PS, ECAL e HCAL), seguido de um sistema de múons (M1-M5).

Figura 3 - Detector LHCb

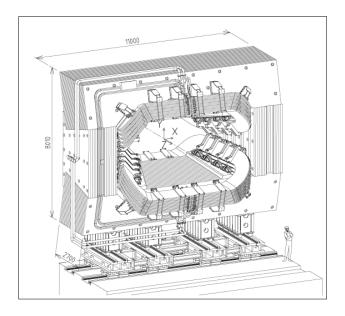

## 3.1 Magneto

Figura 4 - Magneto

Um dipolo magnético, chamado de magneto[9], é usado no experimento LHCb para medida do momento de partículas carregadas, capaz de produzir um campo magnético integrado de 4 Tm. A polaridade do campo magnético pode ser invertida. Esta inversão é usada para o estudo e a redução de erros sistemáticos nas medidas de assimetria. A representação do magneto e o sistema de coordenadas utilizadas pode ser viso na Figura 4.

## 3.2 Sistema de traços

O sistema de traços tem como principal objetivo realizar reconstrução de trajetórias das partículas carregadas, que associada à medida de campo magnético possibilite extrair o momento. O sistema de traços do LHCb é composto por quatro detectores são eles: VELO, TT, IT e OT.

### 3.2.1 VELO

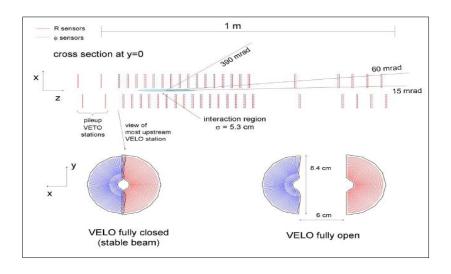

O VErtex LOcator [10] (VELO) é responsável pela medida precisa das coordenadas de traço próximas a região de interação, utilizada para medir a distância entre o vértice de produção dos mesons b e c dos vértices de decaimento. O VELO consiste em uma série de módulos de silício e onde cada módulo promove a medida das coordenadas r e φ, arranjados ao longo da direção do feixe, Figura 5.

Figura 5 - Sub-detector VELO

Os sensores do VELO são localizados a uma distância radial do feixe cuja abertura é menor que a requerida pelo LHC durante a injeção e por esse motivo o sistema é retrátil. Os detectores são montados em um recipiente de vácuo separado dos sensores por uma folha fina e ondulada de alumínio. Isto é feito para minimizar a quantidade de material atravessado por uma partícula antes que esta atravesse o sensor.

#### 3.2.2 Silicon Tracker

Dois detectores formam o Silicon Tracker: O *Trigger Tracker* (TT) e o *Inner Tracker* (IT), ambos utilizam sensores de microtiras, com aproximadamente 200 μm. O detector TT[11] está localizado entre o VELO e o magneto e é composto por duas estações com largura de 150 cm e altura de 130 cm. Cada estação é composta por quatro planos de sensores de silício com espessura de 500 μm. Um sensor é formado por 512 microtiras de silício espaçadas de 183 μm. Isso possibilita uma resolução espacial de aproximadamente 50 μm. As microtiras seguem orientações diferentes em cada plano. No primeiro plano, a orientação é vertical, no segundo plano as microtiras são rotacionadas de -5° na direção do

feixe, no terceiro de 5°, no último as microtiras são dispostas na vertical novamente, por esta geometria esses planos são chamados do tipo x-u-v-x.

O detector IT[12] encontra-se localizado depois do magneto, na região próxima ao feixe, onde se tem maior fluxo de partículas. Os sensores de silício seguem o mesmo *layout* de planos do TT, porém possuem 384 tiras espaçadas de 198 μm.

## 3.2.3 Outer Tracker

Na região mais externa, devido ao menor fluxo de partículas, no OT[13] emprega outra tecnologia de detecção.

O OT é composto por quatro planos de câmaras de arrasto do tipo *Straw tubes*. Cada estação é formada por quatro camadas duplas de tubos. Os *straw tubes* possuem 5 mm de diâmetro e são preenchidos com gás Ar/CO2/O2 = 70%/28.5%/1.5%. A resolução espacial é obtida a partir da medida de tempo entre o sinal do gás e a colisão do LHC.

### **3.3 RICH**

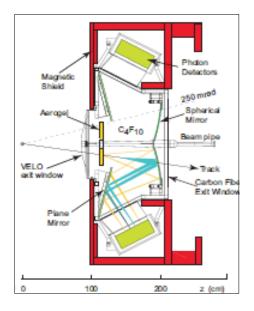

Um dos requerimentos fundamentais do LHCb é a capacidade de separar píons de kaons em um decaimento B. Esta separação é feita através do detector RICH[14] (*Ring Imaging Cherenkov Detector*) numa faixa de momento de 1 a 100 GeV/c. Para esta finalidade existem três tipos de radiadores e dois detectores. O RICH1 localiza-se depois do detector VELO e o RICH2, antes da estação M1. O *layout* destes detectores pode ser observado na Figura 6.

Figura 6 - Sub-detector RICH

No RICH1 são utilizados dois radiadores aerogel e  $C_4F_{10}$ , destinados a partículas de baixo momento. O elemento radiador do RICH2 é o  $CF_4$  destinado a partículas de momento mais alto, variando de 15 a 100 GeV/c.

A luz de Cherenkov produzida nos radiadores é focalizada através de espelhos esféricos no RICH1, e por meio de espelhos planos no RICH2, para a detecção nos detectores de fótons híbridos (HPD – Hybrid Photon Detectors).

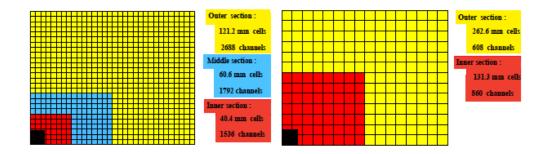

### 3.4 Calorímetros

Os calorímetros[15] realizam muitas funções importantes no LHCb. A primeira consiste na seleção de partículas candidatas para o primeiro nível de trigger (LO), que toma a decisão 4 µs após a interação. São responsáveis também pela discriminação entre fótons, elétrons e hadrons assim como a medida de sua energia e posição. O sistema é composto por quatro detectores: *Scintilator Pad Detector* (SPD), *PreShower detector* (PS), calorímetro eletromagnético (ECAL) e calorímetro hadrônico (HCAL).

A primeira camada de material ativo do calorímetro é o SPD. Sua principal função é detectar partículas carregadas antes da formação dos chuveiros de partículas, permitindo a separação entre fótons e elétrons. Segue-se uma parede 12 mm de chumbo usada para melhor separação de píons e elétrons através da formação e reconstrução de chuveiros eletromagnéticos.

O PS tem o mesmo princípio de funcionamento do SPD, e tem como objetivo definir a posição inicial dos chuveiros.

NO ECAL foi utilizada a tecnologia *Shashlik,* alternando placas cintiladoras de 4 mm e placas de chumbo de 2 mm de espessura.

O HCAL emprega a mesma tecnologia do ECAL porém é composto de placas cintiladoras de 4 mm e placas de ferro de 16 mm de espessura.

O SPD, PS e ECAL contêm 6.000 canais cada um, com três regiões distintas de granularidade ao redor do tubo do feixe, o HCAL contém 1.500 canais e é dividido em duas partes de granularidade distintas.

A variação de granularidade pode ser observada na Figura 7.

Figura 7 - Granularidade dos calorímetros

## 3.5 Sistema de Múons

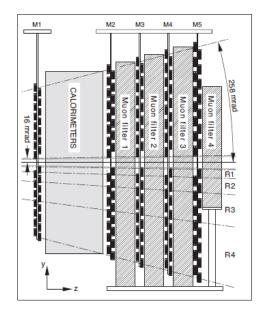

O sistema de múons[16], mostrado na Figura 8, é composto por cinco estações (M1-M5) de forma retangular, situadas ao longo do eixo do tubo do feixe. O sistema é composto por 1380 câmaras, cobrindo uma área total de 435 m². Seu objetivo é fornecer informações para o *trigger* de múons e para a identificação de múons *off-line*.

Figura 8 - Sistema de múons

A estação M1 localiza-se em frente aos calorímetros, próximo ao ponto de interação. É importante para a medida do momento transverso do traço identificado no *trigger* (L0). As outras quatro estacoes (M2-M5) são dispostas atrás dos calorímetros e são intercaladas absorvedores de ferro com 80 cm de espessura para selecionar os múons penetrantes. O momento dos múons para que atravessem as cinco estações é de aproximadamente 6 GeV/c.

## 3.6 Sistema de trigger

Durante a operação do LHC os dados obtidos pela colisão dos prótons são amostrados pelo detector a uma taxa de 40 MHz. Entretanto a velocidade de aquisição de dados é limitada pela eletrônica de cada detector e pela velocidade no armazenamento pelo cluster de computadores disponíveis. Para viabilizar a aquisição de dados um sistema de *trigger*[17] é utilizado para reduzir esta taxa para 2 KHz, selecionando eventos de interesse.

O *trigger* funciona em dois estágios o primeiro chamado de nível zero (LO) e o segundo *trigger* de alto nível (HTL – *High Level Trigger*).

### 3.7 Sistema Online

O propósito do sistema *online*[18][19] é garantir a transferência dos dados da eletrônica próxima aos detectores para os locais de armazenamento permanente. Isto inclui não somente o movimento de dados gerados pelos detectores, a configuração de todos os parâmetros de operação e o monitoramento dos mesmos. O sistema *online* também garante que todos os canais de aquisição do detector estejam propriamente sincronizados com o *clock* do LHC.

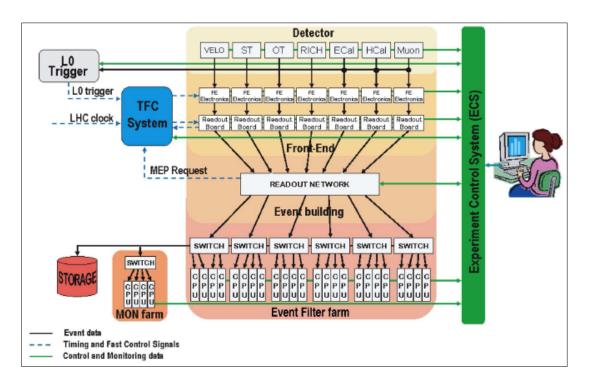

Basicamente o sistema *Online* consiste em três componentes, como mostrado na Figura 9, DAQ (*Data Acquisition System*), o TFC (*Trigger and Fast Control*) e o ECS (*Experiment Control System*).

Figura 9 - Sistema Online

O sistema de aquisição de dados (DAQ) é responsável pelo transporte dos dados pertencentes a um dado *bunch-crossing* identificado pelo *trigger* correspondente ao detector para o local de armazenamento permanente. A arquitetura do DAQ segue como princípios:

Simplicidade: Protocolos simples e um pequeno número de componentes com funcionalidades simples.

- Escalabilidade: Habilidade de reagir a modificações dos parâmetros do sistema, como o tamanho dos eventos, taxas de trigger ou o número de CPUs necessários para o algoritmo de trigger.

- Links ponto a ponto: Nenhum barramento é utilizado (fora das placas). Isto leva a um sistema mais robusto.

- Uso de produtos comerciais quando possível.

Estes princípios permitem a construção de um sistema robusto e confiável com a flexibilidade suficiente para adequar-se a possíveis novos requerimentos, motivados pela experiência com dados reais.

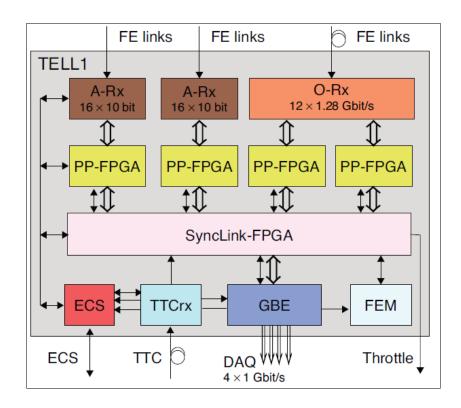

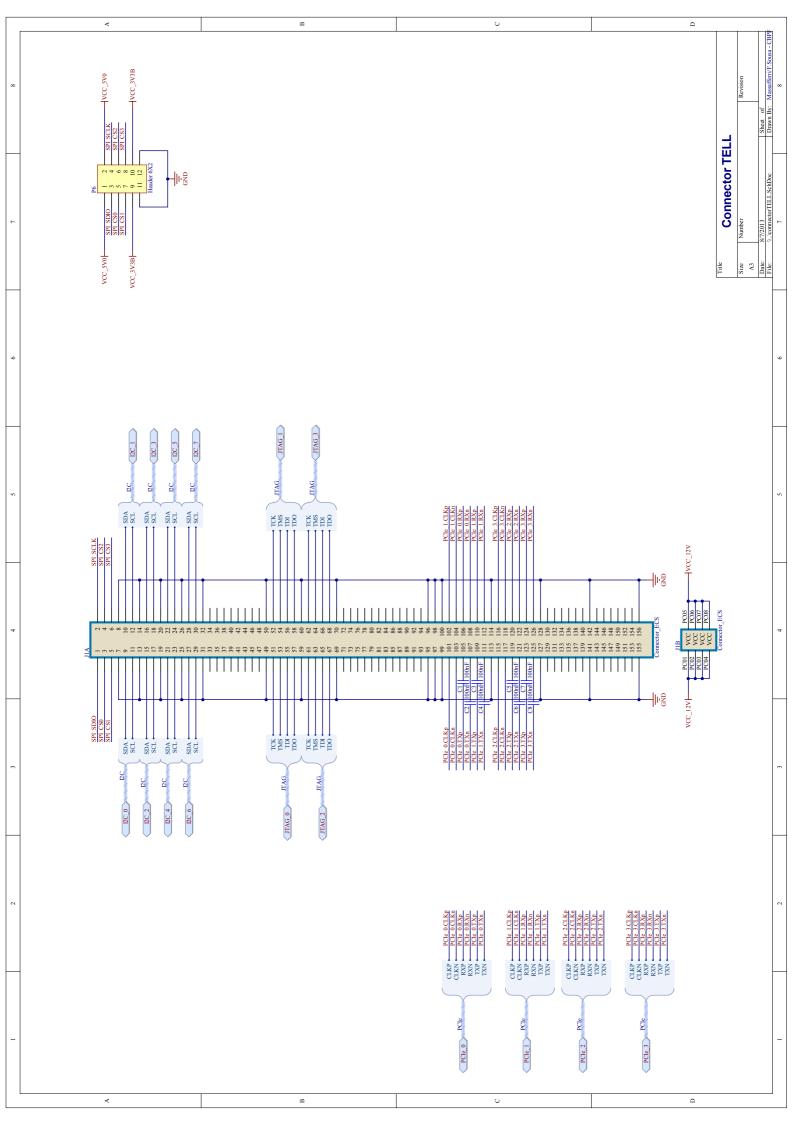

Os dados coletados pelos módulos da eletrônica próxima aos detectores do LHCb são coletados por placas de *readout* denominadas TELL1.

Os dados são recebidos pela placa TELL1 da eletrônica próxima aos detectores através de placas com links ópticos ou analógicos e processados em quatro FPGAs. Nas FPGAs um processamento de modo comum, *zero-suppression* ou compressão de dados, é realizado dependendo das necessidades individuais dos detectores. O resultados dos fragmentos dos dados são coletados por um quinto FPGA (*SyncLink*) e formatados em um pacote *raw* IP. Este enviado ao sistema de aquisição de dados através de uma placa de quatro canais *Gigabit-Ethernet*. A interface com o ECS é feita através de um CCPC montado como *mezzanino* na TELL1. Os sinais de sincronismo e *clock* são transmitidos através da interface de *Trigger, Timing and Control* (TTC). O fluxo de dados para o TFC é realizado através do sinal de *trottle* e é conduzido pelo FPGA *SyncLink*. O diagrama de blocos simplificado é apresentado na Figura 10.

Figura 10 - Diagrama de blocos simplificado da TELL1

No cluster de CPU[20], o algoritmo HLT seleciona as interações de interesse em consequência de uma decisão positiva. Os dados são enviados então para o local de armazenamento permanente. Com o uso do HLT é esperada a redução da taxa global de trigger de 1 MHz para aproximadamente 2 KHz. O local de armazenamento permanente tem a capacidade de aproximadamente 40 TB, oferecendo um espaço de buffer suficiente para lidar com possíveis interrupções de transferências para o local de armazenamento permanente principal do CERN. Para a transferência de dados foi escolhida a tecnologia para links Gigabit Ethernet, principalmente devido a sua ampla utilização e aceitação no mercado de redes LAN, o que inclui seu baixo custo de aquisição. A grande variedade de velocidades de 10Mb/s a 10Gb/s e a disponibilidade de switches com grande capacidade de portas são outras características que foram levadas em consideração.

As quatro portas *Gigabit Ethernet* da placa TELL1 são usadas como estágio de saída. Algumas destas são conectadas a um grande switch de rede, fornecendo a conectividade entre a TELL1 e nós individuais do *Cluster*. Para superar um *overhead* significativo por pacote de *Ethernet*, o conceito de MEP (*Multiple Event Packets*) foi concebido. Em torno de dez pacotes de dados provenientes de diversas decisões de *trigger* são coletados em um único pacote IP e por sua vez transferidos de uma só vez pela rede. O tamanho do *cluster* de *CPU*

executando o algoritmo do HLT é determinado pela média de tempo de execução por evento, mas também possivelmente determinada pelo número máximo de banda em um nó de processamento individual. Se o tempo de execução for muito baixo, a banda de entrada pode constituir um fator limitante e o número de nós deve ser aumentado. O algoritmo HLT é executado em um *Cluster* de *CPU* bastante grande, onde se espera um número de 1000 a 2000 servidores do tipo 1U contendo *CPUs* com tecnologia *multi-core*. O tamanho inicial do cluster era de apenas 200 servidores e a máxima capacidade para instalação é de 2200 unidades. Este grande número de servidores esta organizado em 50 *sub-clusters* de 20 a 40 *CPUs* cada. A escalabilidade é garantida desde que um *sub-cluster* seja uma unidade funcional e não haja comunicação cruzada entre os *sub-clusters*.

A qualidade dos dados adquiridos é checada em um *cluster* de monitoramento separado que recebe os eventos aceitos pelo HLT e executa algoritmos definidos como por exemplo, o monitoramento da eficiência dos canais e a resolução de massa de um detector.

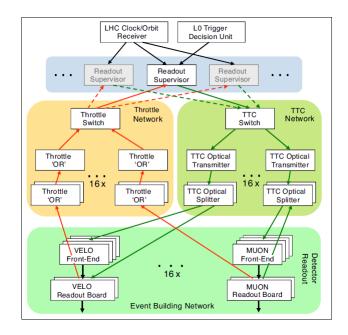

O sistema TFC trata todos os estágios do readout de dados entre a eletrônica de front-end e o cluster de processamento do sistema online, distribuindo o clock de sincronismo do feixe, as decisões do trigger LO, sinais síncronos de reset e comandos de fast control. O sistema é uma combinação de componentes eletrônicos comum a todos os experimentos do LHC e da eletrônica particular do LHCb. A arquitetura do TFC é mostrada na Figura 11 e pode ser descrita em temos de três componentes principais; a rede de distribuição do TFC, a rede de trigger throttle e o TFC máster, também conhecido como Readout Supervisor.

Figura 11 – Arquitetura do sistema TFC

A rede óptica de distribuição do TFC, assim como os transmissores e receptores, é baseada no sistema TTC do LHC desenvolvido no CERN. Além de transmitir o *clock* de sincronismo do feixe, o protocolo tem como característica a baixa latência do canal de *trigger* e um segundo canal com informações usadas para transmissão de comandos de controle codificados. Um switch foi desenvolvido e introduzido na rede de distribuição para permitir o particionamento dinâmico do LHCb, suportando as atividades independentes e concorrentes das atividades dos detectores, assim como verificação, calibração e teste.

A rede óptica de *throttle* é usada para transmitir o sinal de *back-pressure*, isto é, a inibição do sinal de *trigger*, para as partes assíncronas do *readout* para o *Readout Supervisor* em caso de congestionamento do caminho de dados. A rede incorpora um switch para suportar o requerimento de que o sistema de *readout* seja particionável e para permitir que os módulos executem a operação logica *OR* (OU) do sinal de *throttle* de cada subsistema localmente.

O elemento principal do TFC é o *Readout Supervisor*. Sua função é fazer a interface entre o sistema de trigger do LHCb e a cadeia de *readout*. Este elemento sincroniza as decisões de *trigger*, os comandos de sincronismo de feixe ao *clock* e o sinal da orbita do feixe, providos pelo LHC. Outra característica é a capacidade de produzir uma variedade de *auto-triggers* para a calibração e teste dos detectores, além de e realizar o controle de *trigger* em função da carga do *readout*. A fim de executar um balanceamento dinâmico da

carga sobre os nós do *cluster*, o *Readout Supervisor* seleciona e retransmite o destino do próximo grupo de eventos para as placas de *readout* baseado em um esquema de crédito em que cada nó do *cluster* envia os dados solicitados diretamente para o *Readout Supervisor*.

Para cada evento de *trigger* o *Readout Supervisor* transmite os dados pela rede dos *readout. E*ste será anexado com os dados do evento, contendo o identificador do evento, o tempo e a fonte de onde o *trigger* foi gerado.

O ECS garante o controle e monitoramento operacional de todo LHCb. Isto engloba não somente o controle tradicional de domínio do detector, como também o controle de alta e baixa tensão, temperatura, fluxo de gases, pressões, controle e monitoramento do *Trigger*, TFC e do Sistema de aquisição. Os componentes de *hardware* do ECS são um tanto diversos, principalmente em consequência da variedade de equipamentos que necessitam ser controlados, como *crates* padronizados e fontes de alimentação. No LHCb, um grande esforço foi feito para minimizar o número de diferentes tipos de interface e barramentos de conexão. São encontrados:

- SPECS (Serial Protocol for ECS) é um barramento serial de alta velocidade (10 Mb/s)

- CAN (Controller Area Network)

- Ethernet

Os dois primeiros, SPECS e CAN, são utilizados em equipamentos instalados na área de alta radiação próxima ao detector. Estas interfaces toleram um certo nível de radiação, porém não são construídos para este fim. Conexões *Ethernet* são somente utilizadas em áreas livres de radiação. A *Ethernet* é usada para controlar não somente computadores, mas também placas TELL1 através de um CCPC montado diretamente em cada placa. Esta escolha permite que computadores com interfaces comuns de rede controlem a eletrônica de *readout*.

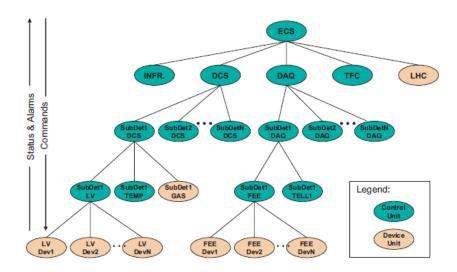

O *software* de controle do ECS é baseado no PVSS II, um sistema comercial SCADA (Supervisory Control And Data Acquisition). Este *toolkit* fornece a infraestrutura necessária para a construção do sistema ECS, como a banco de dados da configuração do detector, a

comunicação entre componentes distribuídos, bibliotecas gráficas para a operação de painéis e um sistema de alarmes. Baseado no PVSS, um sistema hierárquico e distribuído foi desenvolvido como mostra a Figura 12.

Figura 12 - Sistema hierárquico e distribuído

As *Device Units são* os componentes de acesso de baixo nível que modela os dispositivos físicos e tipicamente comunicam diretamente com o *hardware*. De uma maneira geral é implementado uma máquina de estado simples executada pelo controlador *Control Unit*. Exemplos de *Device Units* são: Fontes de alimentação e processos de *software*, como o HLT.

As transações e estados de alto nível são implementados nas *Control Units* que também contém a lógica local para a recuperação de erros de uma *Device Unit* Subordinada. Típicos exemplos de *Control Units* são: O sistema de Alta tensão, ou componentes que controlam *crates* de um detector ou todo o cluster de filtragem de eventos. As *Control Units* podem sem controladas por outras *Control Units*, para permitir a construção de uma hierarquia de profundidade arbitrária. O sequenciamento de estados é conseguido com o uso de um pacote de máquina de estados finito, baseado no SMI++ que permite a criação de uma lógica complexa. Os componentes distribuídos do sistema ECS são conectados através de uma larga rede *Ethernet*, constituída de centenas de links *Gigabit Ethernet*.

## 4. Upgrade da eletrônica e sistema online do LHCb

Para que seja possível implementar a aquisição de dados como previsto no *upgrade* do LHCb[21] deve-se modificar a arquitetura da eletrônica[22]. A atual arquitetura, inclui um *buffer* em *pipeline*, impondo um limite na taxa de aquisição e de *trigger* de 1 MHz. Qualquer aumento acima desta taxa requer uma nova arquitetura. Para atingir taxas de 40 MHz necessita-se do uso de tecnológicas modernas que se adaptem ao uso na física de altas energias. Por exemplo, *links* ópticos de alta velocidade serão instalados para acomodar o aumento do volume de dados vindos do detector, assim como novos esquemas de compressão de dados que serão implementados para reduzir o número de *links*. Embora o objetivo seja eliminar o *trigger* baseado em *hardware*, um mecanismo de controle será desenvolvido para controlar o fluxo de dados na aquisição. Este controle poderá ser aprimorado com informações da física, da mesma maneira do mecanismo de *trigger* existente no *Level-O, LLT (Low Level Trigger)*.

Embora o *upgrade* exija grandes modificações na eletrônica do detector, algumas medidas estão sendo tomadas para minimizar o custo, tempo de desenvolvimento e esforço na instalação, são eles:

- Reuso das partes existentes na eletrônica de FE que satisfaçam os requerimentos do upgrade.

- 2. Desenvolvimento de módulos e dispositivos comuns usados por todos os detectores.

- 3. Reutilizar o máximo possível da infraestrutura existente.

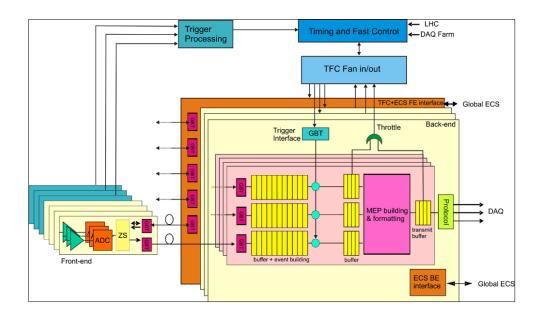

Figura 13 - Arquitetura geral do upgrade na eletrônica

A arquitetura geral do upgrade na eletrônica é mostrada na Figura 13. A eletrônica de FE sujeita a radiação, localizada junto aos detectores, é responsável pela amplificação e condicionamento do sinal gerado nos detectores. Estes sinais são digitalizados, comprimidos, formatados e então transmitidos via *links* de ópticos de alta velocidade. A eletrônica de *Back-End* (*BE*) baseada nas placas de aquisição TELL40 localiza-se em uma área protegida, afastada da radiação, e recebe os dados através dos *links* ópticos. Após a filtragem pelo LLT, os dados são digitalizados para transmissão através do sistema de aquisição de dados.

A transmissão da informação do *trigger* é feita pelo sistema TFC e contém o número de identificação de *bunch-crossing* onde o LLT teve uma decisão positiva. A configuração e monitoramento da eletrônica de BE e FE é feita através da interface ECS.

Links genéricos estão sendo desenvolvidos para o upgrade dos experimentos do LHC. Um mesmo link pode ser usado para a aquisição de dados, TFC e ECS. Por razões de custo e flexibilidade, os dados provenientes dos detectores serão transmitidos em links unidirecionais enquanto as funcionalidades de TFC e ECS irão se juntar em um número menor de links bidirecionais.

A estrutura de *bunch* do LHC será constituída de 3564 *bunches* espaçados por 24.95 ns. *Resets* regulares dos sistemas irão ser gerados para garantir o sincronismo e minimizar a perda de dados.

A taxa de ocupação de dados na banda disponível será determinada pela intensidade de colisões próton-próton no LHCb dominada pelo ruído do detector e da eletrônica. A energia nominal instantânea planejada para o upgrade e de 1 x 10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>.

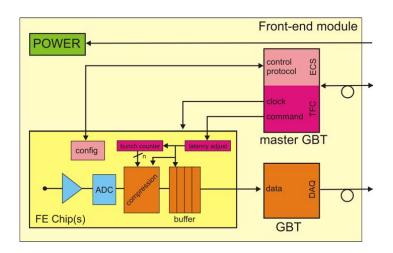

## 4.1 Eletrônica de Front-end

Um típico módulo de FE pode ser visto na Figura 14. Estes módulos consistem basicamente em circuitos integrados com a eletrônica de aquisição do FE conectados a *links* ópticos de alta velocidade bidirecionais, implementados usando o GBT (*Gigabit Bidirectional Trigger and Data link*) [23]. Os circuitos integrados da eletrônica de FE devem ser tolerantes a radiação presente no ambiente do detector. Áreas de alta radiação algumas vezes requerem circuitos integrados desenvolvidos sob medida. Entretanto, dispositivos encontrados comercialmente poderão ser utilizados desde que provem ser tolerantes aos níveis de radiação esperado.

Figura 14 - Típico módulo de FE

Espera-se que o circuito integrado do FE deva ser capaz de amplificar, condicionar e digitalizar o sinal gerado pelo detector de acordo com seus respectivos requerimentos. O tempo total para a execução da aquisição dos sinais nestes circuitos deve ser rápido suficiente para permitir a identificação de uma colisão com o seu *bunch crossing*, enquanto que o tempo de recuperação para uma próxima colisão deve seguir as específicações do detector em questão. Cada detector deverá escolher o seu método de conversão analógico-digital dos sinais de forma a melhorar o desempenho, complexidade e custo.

Os circuitos digitais serão sincronizados com o *clock* de 40 MHz proveniente do GBT. O circuito deverá também permitir o ajuste de fase do *clock* para otimizar sua eficiência, respeitando colisões com espaços de 25 ns. O tamanho dos circuitos de armazenamento deverá ser tal que seja capaz de absorver flutuações estatísticas no tamanho de um evento comprimido para fazer um uso eficiente da largura de banda fornecida pelo GBT. Isto implica que dados de diferentes módulos de FE irão ser enviados de forma assíncrona para os módulos de BE. Informações adicionais serão adicionadas posteriormente nos pacotes de dados permitindo assim a reconstrução de eventos completos. A formatação mínima necessária é anexada ao cabeçalho do pacote contendo bits do *bunch-counter* (BXID). O BXID deverá ser gerado no circuito integrado do FE de forma síncrona em referência ao *clock*. Estes bits serão usados para rastrear os dados posteriormente no sistema.

Após o pacote estar completo, os dados serão enviados para a interface de DAQ do circuito integrado GBT e, em sequência, transmitidos via links ópticos.

# 4.2 Arquitetura geral da interface TFC/ECS no Front-end

Os sinais de controles e sincronismo do sistema serão enviados através dos links GBT da área protegida de radiação pelo *master-GBT*. Um pacote de dados será transmitido a cada período de 25 ns e transmitidos simultaneamente para todos os módulos de FE. Este pacote deverá ser decodificado pelo circuito integrado de FE e deverá se encarregar de algumas tarefas. As mais importantes serão:

- 1. Gerar o sinal de reset nos FE.

- 2. Gerar o pulso de calibração.

- 3. Gerar o sinal de reset para o contador BXID.

Para sincronizar o sistema devido a utilização de diferentes comprimentos de links, cada circuito integrado deverá ser capaz de atrasar os comandos do TFC por até 16 ciclos de *clock*. Isto permitirá a correção de qualquer diferença de latências entre os dispositivos do FE conectados ao mesmo barramento de comandos do TFC.

A configuração dos circuitos integrados do FE será feita pela interface ECS encontrada no circuito integrado do GBT-SCA[24]. Os circuitos integrados de FE deverão suportar ao menos um dos protocolos padrões disponíveis no GBT-SCA para este fim. Para permitir a leitura dos dados recém-configurados ou para qualquer outro tipo de verificação destes dados. Cada link de ECS deverá ser implementado como um link ponto-a-ponto entre o sistema do GBT e os dispositivos de FE.

Os protocolos padrões disponíveis no circuito integrado GBT-SCA são:

- Até 16 controladores l<sup>2</sup>C

- Um controlador JTAG

- 32 canais de conversores A/D (Multiplexados)

- Um barramento de memória de 32 bits

- Até 4 controladores PIA (Parallel Interface Adapter)

- Um barramento SPI

- Até 4 canais de conversores D/A

A largura de banda disponível no GBT para a transmissão de informações ECS/TFC é grande, então, em muitos casos será mais eficiente o uso de um link bidirecional GBT para fornecer informações de ECS/TFC para muitos módulos de FE.

## 4.3 Placas de readout

Para acomodar os novos requerimentos do *upgrade*, o sistema de aquisição e controle atual também deverá ser modificado. Uma placa genérica que cobre todos os requisitos necessários está sendo desenvolvida pelo CPPM[25].

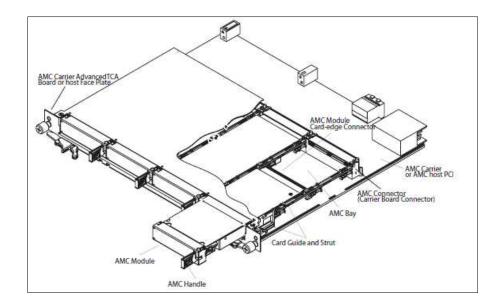

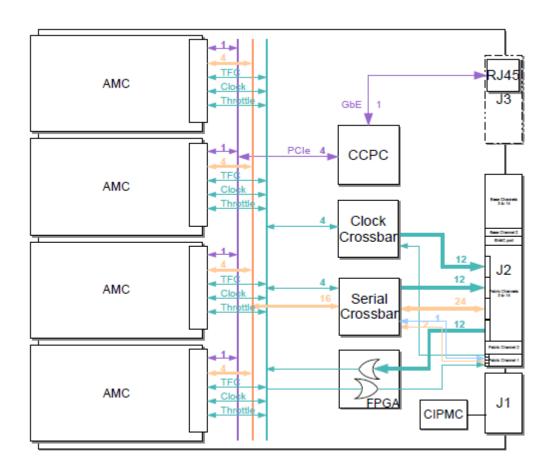

Dois componentes genéricos estão em fase de desenvolvimento para formar uma placa de *readout* compatível com o padrão ATCA[26], mostrada na Figura 15. São elas:

AMC40: terá a capacidade de comunicar-se com a eletrônica de FE e Clusters de processamento.

• ATCA40 : placa-mãe que hospeda até quatro placas AMC40 como *mezzanino*.

Figura 15 - Placa ATCA com quatro módulos AMC

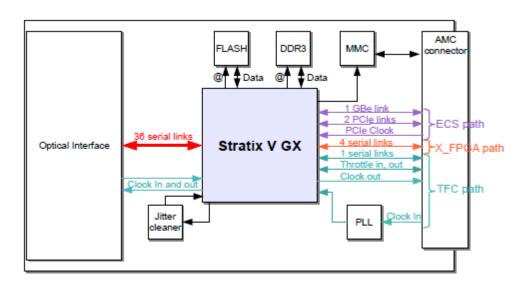

A placa AMC40 está sendo desenvolvida para ser capaz de processar até 36 links ópticos de entrada e até 36 links ópticos de saída, em alta velocidade, através do *transceiver* do FPGA Stratrix V GX. Cada link deverá ser capaz de transmitir ou receber até 10 Gbits/s de dados. Um diagrama de blocos simplificado pode ser visto na Figura 16.

Figura 16 - Arquitetura da placa AMC40

O FPGA gerencia três tipos de caminhos através do conector AMC

- O caminho do ECS que pode ser através da conexão Gigabit Ethernet ou PCIe.

- O caminho entre as FPGAs feito através de quatro links seriais.

O caminho do TFC feito por linhas de clock bidirecionais, linhas LVDS para transmissão de informações de throttle e links seriais de alta velocidade.

Os caminhos de ECS, TFC e *inter-FPGA*, descritos anteriormente, são gerenciados pela placa ATCA40. Seu diagrama de blocos pode ser visto na Figura 17.

Figura 17 - Placa ATCA40

Um barramento de *clock* (*Clock Crossbar*) permitirá o roteamento do clock entre as placas AMC e o conector J2, ou entre placas AMC. O Barramento serial (*Serial Crossbar*) permitirá o roteamento dos links seriais de alta velocidade entre as placas AMC e o conector J2, ou entre placas AMC.

## 4.3.1 ECS nas placas de readout

Um CCPC poderá ler ou escrever registradores localizados dentro da FPGA através de quatro barramentos PCIe conectados as placas AMC. O CCPC deverá executar como sistema operacional o Linux e também será responsável pelo controle do *link Ethernet* com o sistema supervisório externo. Este é o principal componente que faz a ligação destas placas com o sistema ECS global. Um switch externo irá permitir o acesso a todos os CCPCs da mesma maneira que se faz na atual arquitetura encontrada nas placas TELL1.

Similarmente com a eletrônica de FE, os softwares de configuração e monitoramento das placas de *readout* deverão ser fornecidos centralmente:

- Bibliotecas de baixo nível e ferramentas de linhas de comando para os CCPC nas placas irão permitir o acesso a diferentes chips encontrados na placa de readout e seus mezzaninos.

- Um servidor executado no CCPC irá permitir a comunicação via TCP/IP e implementará comandos de alto nível para a configuração e monitoramento de diversos chips.

A integração com o componente ECS via WinCC-AO (ex PVSS) irá fornecer uma descrição de alto nível e acesso a todos os componentes eletrônicos.

O sistema ECS da placa de *readout* é o foco deste trabalho e no capítulo a seguir serão descritos todos os elementos necessários para o desenvolvimento deste sistema.

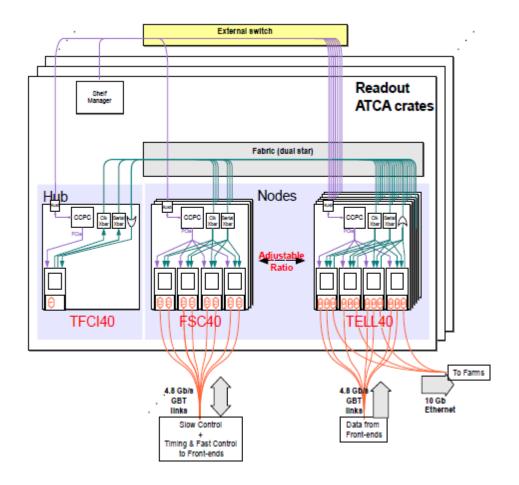

# 4.4 Arquitetura de readout

O fluxo de dados do ECS e TFC irão requerer links bidirecionais enquanto a aquisição será feita por links unidirecionais. Os FE em geral irão necessitar de menos links para ECS e TFC do que links para aquisição. O *crate* que gerenciará um detector poderá ajustar a relação entre o número de placas de *slow control* (FSC40) e aquisição(TELL40) para atingir o número de FE necessárias na eletrônica de FE, como mostrado na Figura 18.

Figura 18 - Arquitetura de readout com switch externo

Cinco configurações podem ser tratadas com o mesmo hardware:

- TELL40 para aquisição de dados.

- FSC40 para slow control e interfaceamento TFC com os FE.

- ODIN40 para Supervisão do TFC, decisões de trigger de baixo nível e interface com o tempo do LHC.

- TFCI40 para o gerenciamento local do TFC em cada crate.

- TRIG40 para fornecer interface entre o antigo trigger LO, o sistema de TFC e DAQ

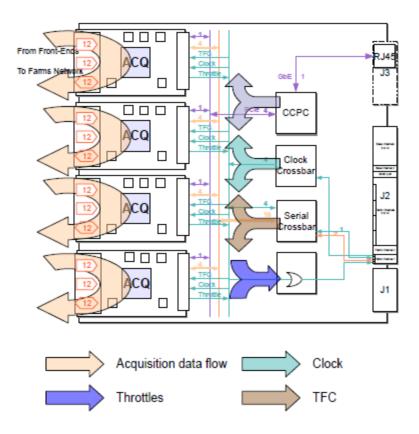

Na configuração TELL40, o sistema será capaz de coletar fragmentos de um evento da eletrônica de FE e juntá-los em um único pacote Ethernet que será enviado para o cluster de processamento. Três caminhos diferentes são ilustrados pela Figura 19.

Figura 19 - Configuração TELL40

Os fragmentos dos eventos serão processados no FPGA da placa AMC40. Informações de *clock* e TFC serão recebidas pela placa TFCI40 localizadas no mesmo *crate*. E então distribuídas para as placas TELL40 através do *backplane* do *crate* e distribuídas para os FPGA da placa AMC40 pelo barramento local. Nesta configuração as informações de *clock* e TFC serão utilizadas pelo processamento local da TELL40. A informação de *throttle* gerada por cada placa AMC40 será então concatenada e enviada de volta para a única placa TFCI40.

Os dados do ECS das placas AMC40 serão recebidos pelo CCPC via rede dedicada e transmitidas para os FPGAs localizados nas placas AMC40 através dos links PCIe.

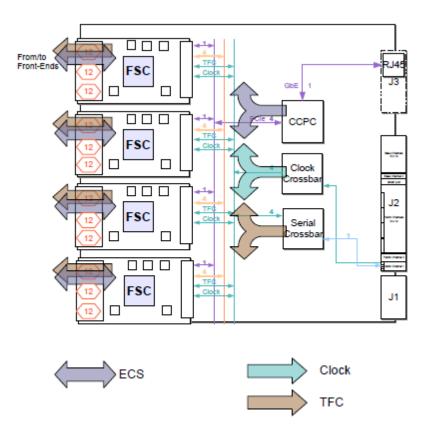

A placa na configuração FSC40 atuará como concentrador do ECS/TFC, os caminhos diferentes desta configuração podem ser visto na Figura 20.

Figura 20 - Configuração FSC40

Os dados do ECS e TFC serão recebidos e transmitidos de forma similar a TELL40. Porém, todas estas informações serão concatenadas para serem enviadas pelo *link* GBT para os FE. Um mecanismo especial, embarcados nas FPGA, irá garantir que a fase do *clock* seja constante respeitando o principal com a precisão de 50 us RMS.

Até 144 links ECS poderão ser controlados por uma placa FSC40.

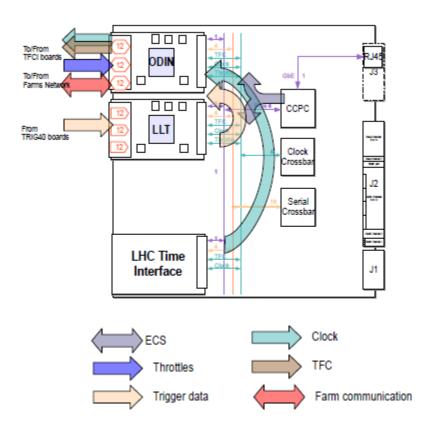

ODIN40 é o componente principal que tratará dos sinais de clock e distribuição de comandos. Sua configuração pode ser observada na Figura 21.

Figura 21 - Configuração ODIN40

O clock do LHC será recebido por uma placa dedicada (LHC Time Interface) e será enviado para a placa ODIN/AMC40 através da rede de clock local e seu crossbar associado. Os triggers candidatos do LLT serão computados pela placa TRIG40 e recebidos pela placa LLT/AMC40 que controlará a decisão final do LLT e o enviará para a placa ODIN/AMC40 através dos links seriais de alta velocidade que interconectam as diferentes placas AMC.

A função *Super*-ODIN, implementada na placa ODIN/AMC40, usa a decisão principal do LLT, a informação de *throttle* da placa TELL40 e a disponibilidade do cluster de processamento, para construir a informação do TFC que serão transmitidas pelas fibras ópticas para a placa TFCI40 em cada *crate*. Estra transmissão será feita sincronamente com o *clock* do LHC e em fase constante.

Até 24 *crates* poderão ser tratados por uma placa *Super*-ODIN. A comunicação com os *cluster* de processamento será feito por meio de 12 links ópticos bidirecionais usando o protocolo 10 Gb Ethernet.

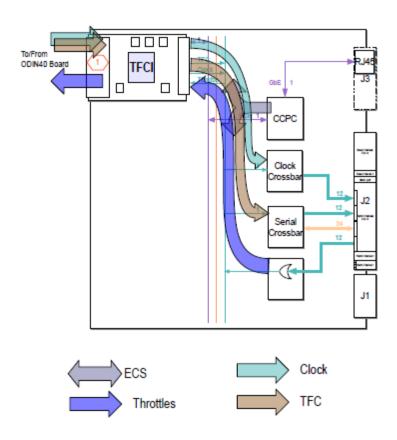

A placa TFCI40 será a interface entre a placa ODIN40 local do *crate*. Sua configuração pode ser encontrada na Figura 22.

Figura 22 - Configuração TFCI40

As informações de *clock* e TFC serão recebidas pelos módulos ODIN40 através de links ópticos, e assim distribuídas para outras placas no mesmo *crate* (FSC40, TELL40 TRIG40) via ao *backplane* com ajuda do *crossbar* localizado na placa ATC40. Informações de *throttle* oriundas de placas TELL40 sofrerão a operação logica "OU" localmente e enviadas para a placa ODIN40 via *link* óptico.

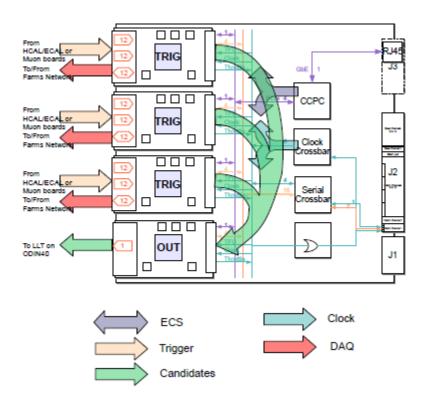

A interface entre os processadores LLT de múons e dos calorímetros, e unidades de decisão LLT localizadas na placa ODIN40 será feita através da configuração TRIG40, ilustrada na Figura 23.

Figura 23 - Configuração TRIG40

O processadores de LLT enviarão os seus candidatos a placa TRIG/AMC40 a um taxa de 40 Mhz. Candidatos com o maior momento transverso serão selecionados. Os restantes serão enviados para a placa OUT/AMC40 pelos links ópticos, aonde a decisão final será tomada.

Os processadores de LLT enviarão os dados de entrada e os resultados do processamento a 1 MHz. Esta informação será escrita em disco e usada para verificar o comportamento do processador. Estes dados brutos serão recebidos pela placa TRG/AMC40 onde serão concatenados e comprimidos para posterior envio para o DAQ.

## 5. O Módulo ECS-CBPF

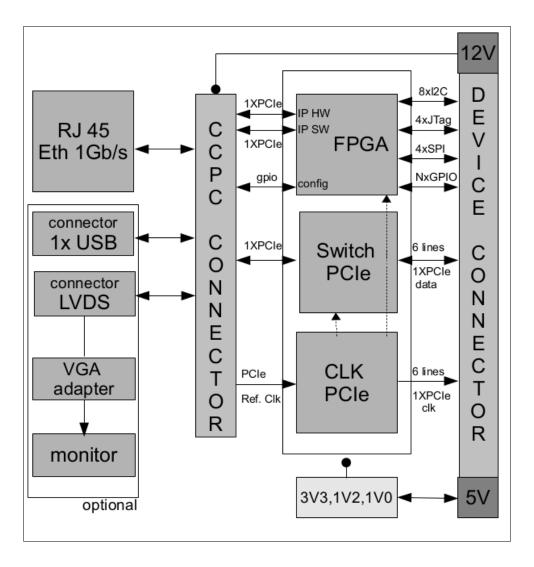

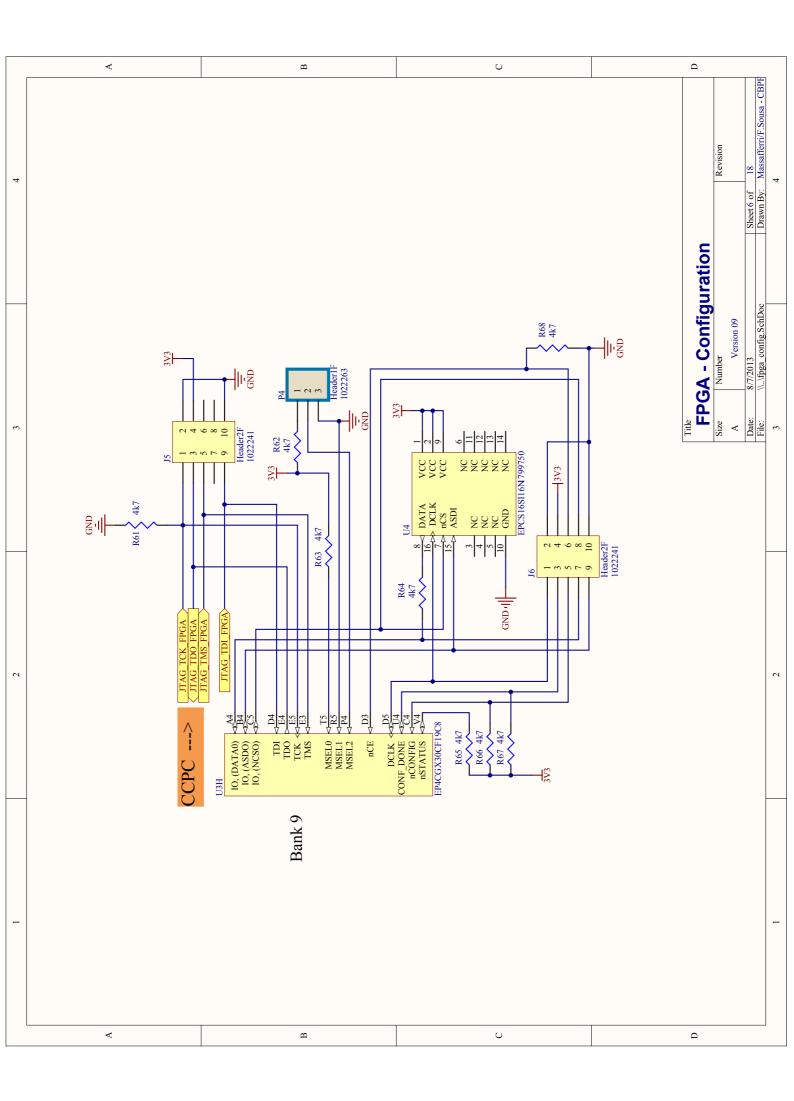

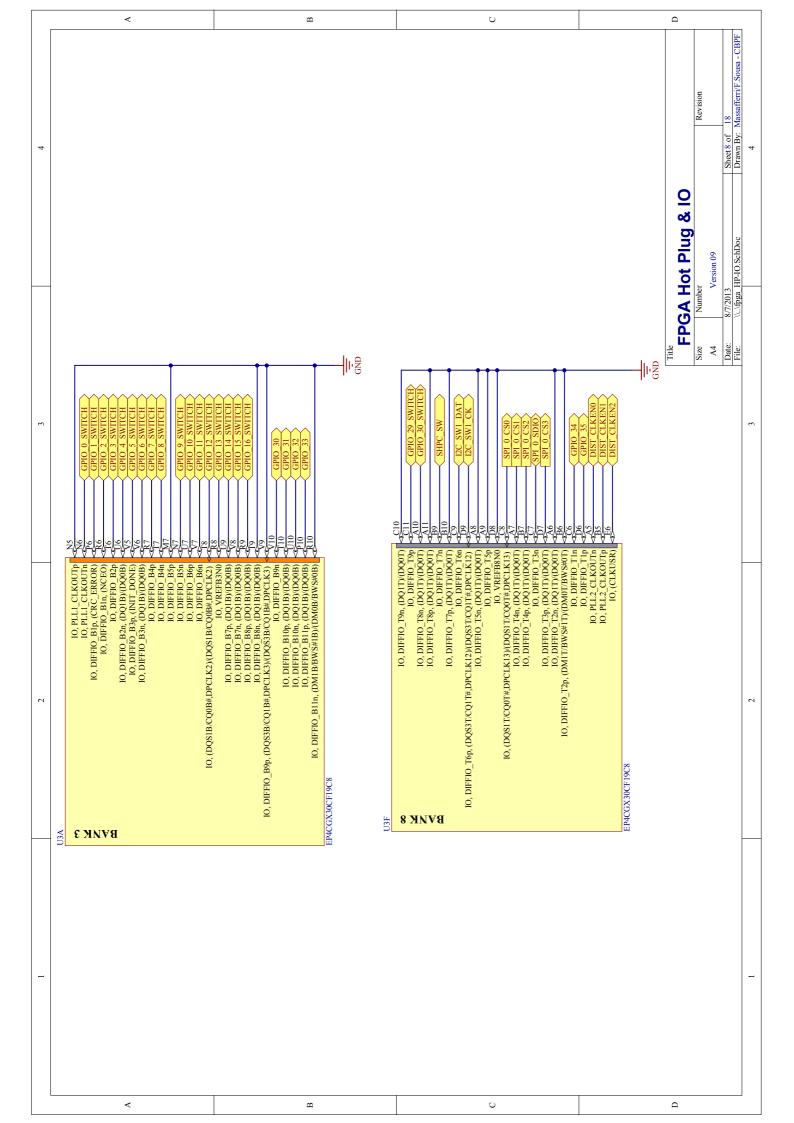

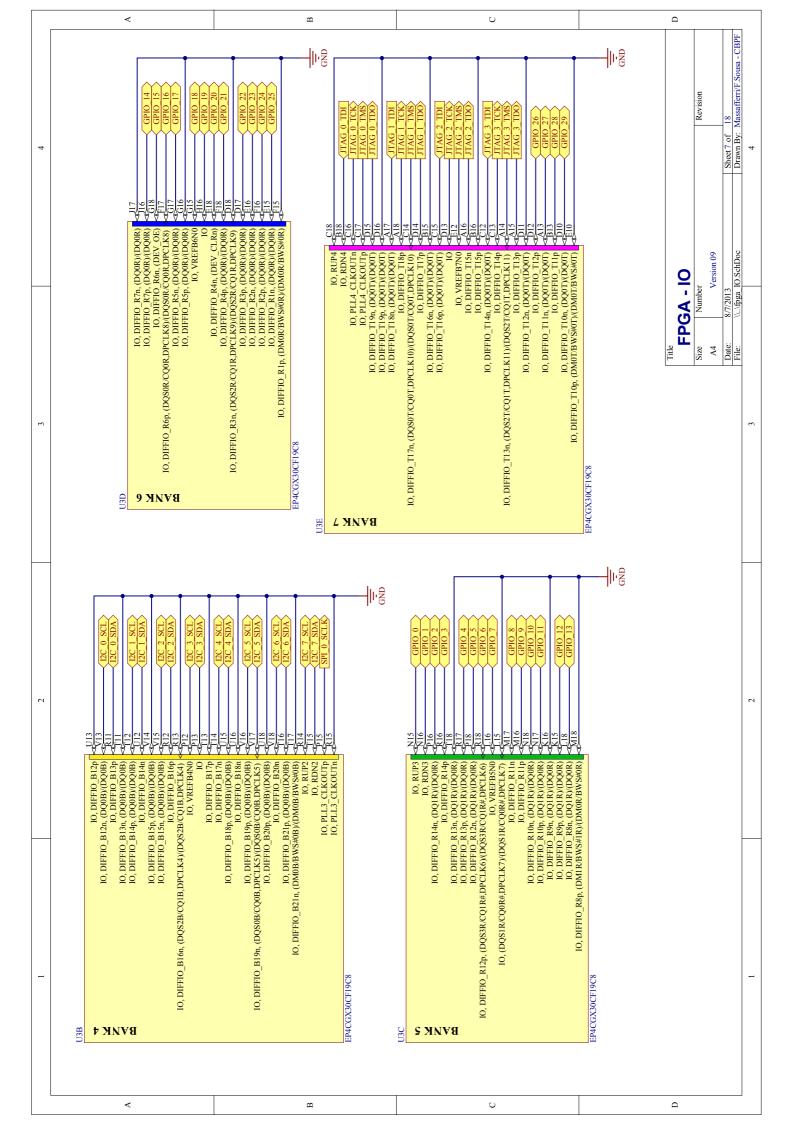

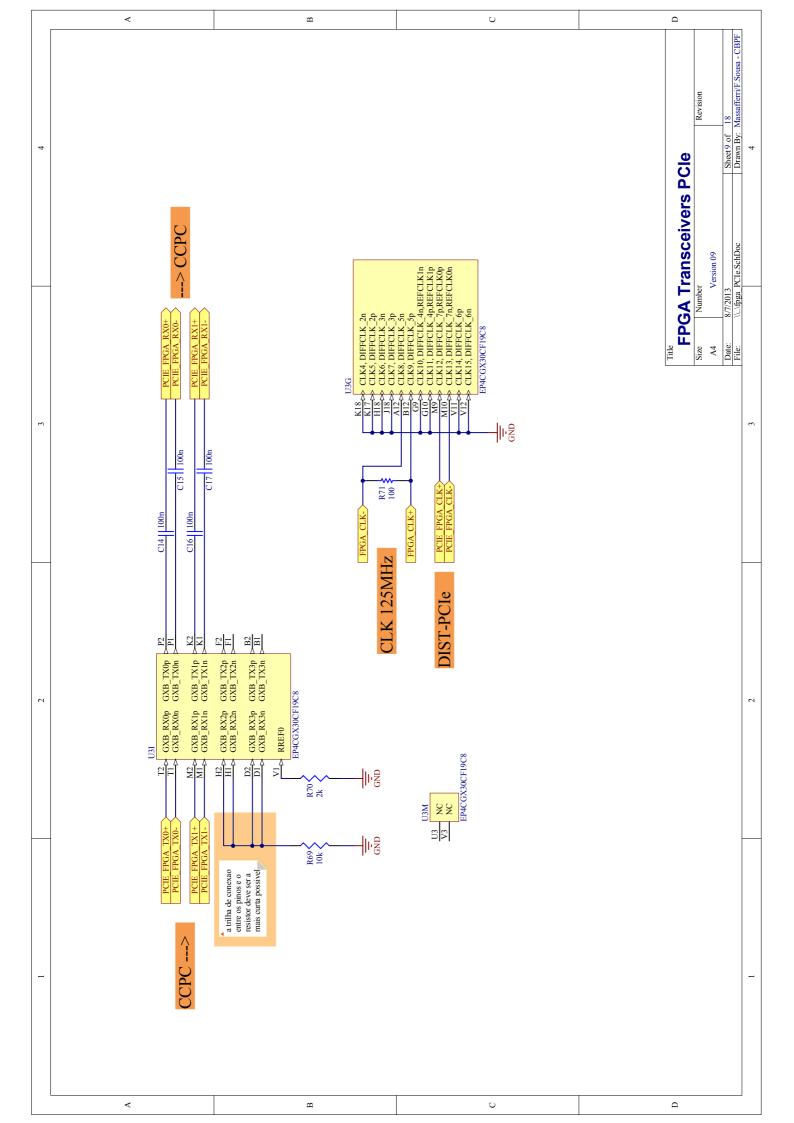

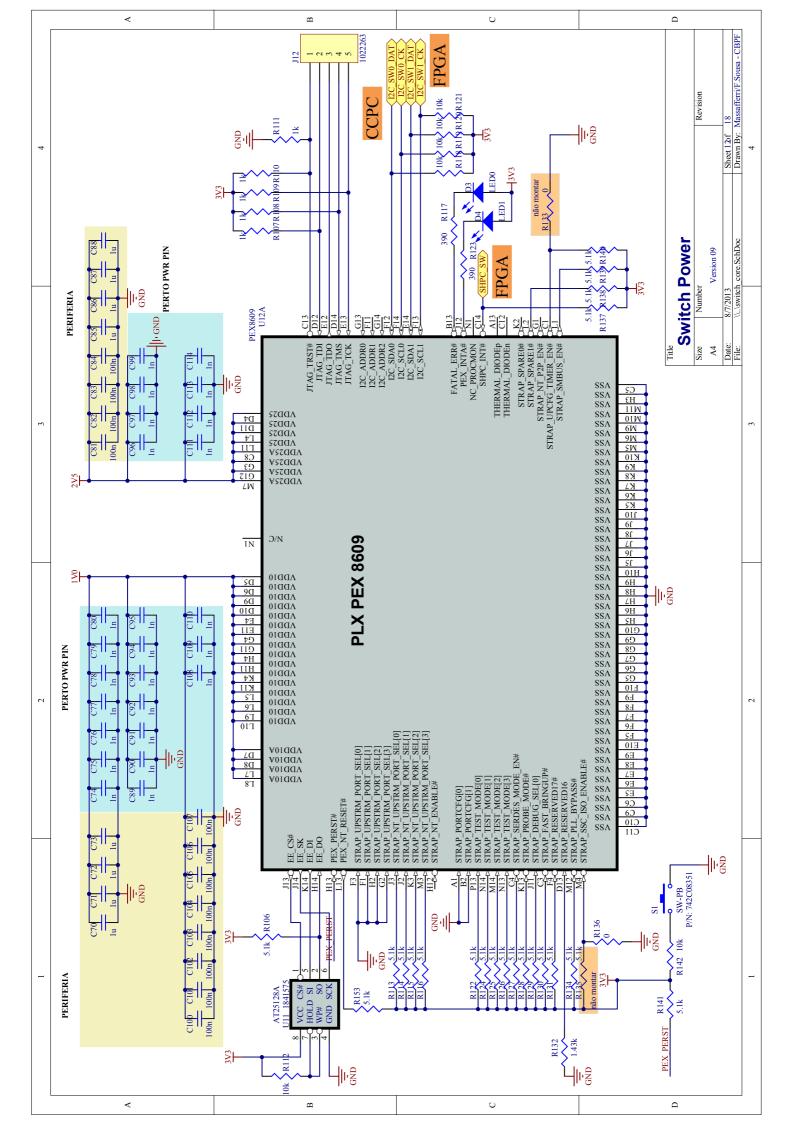

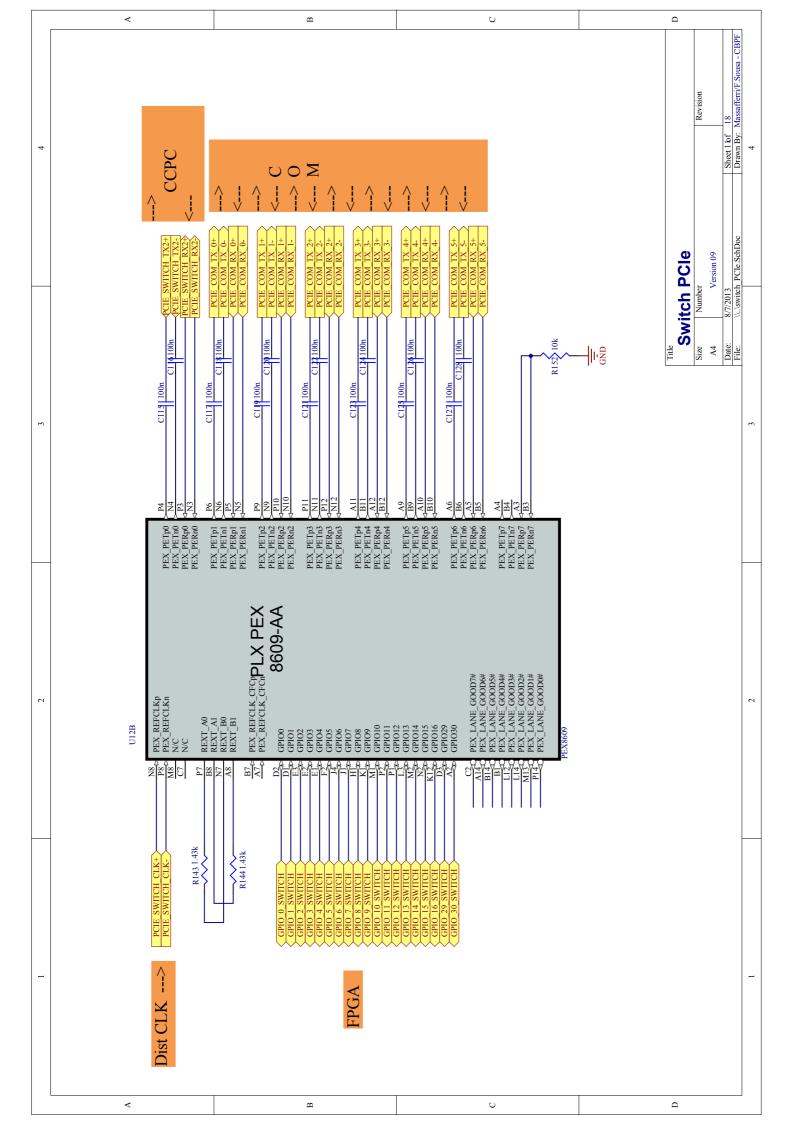

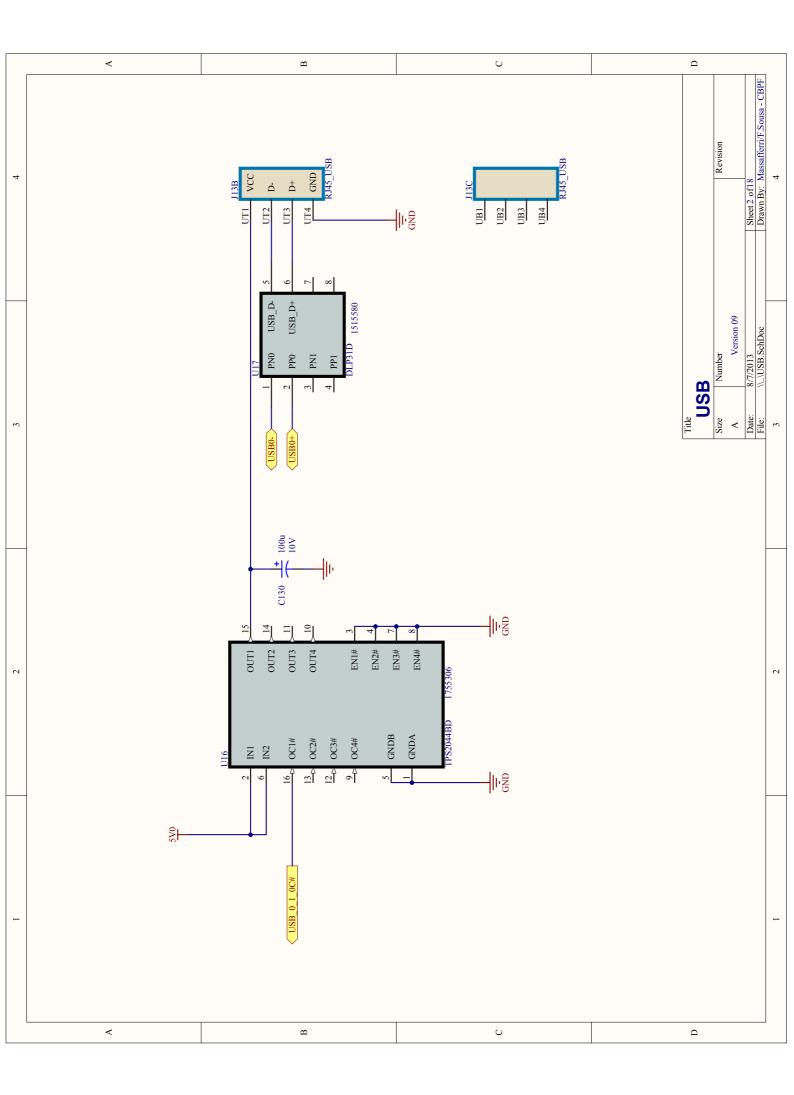

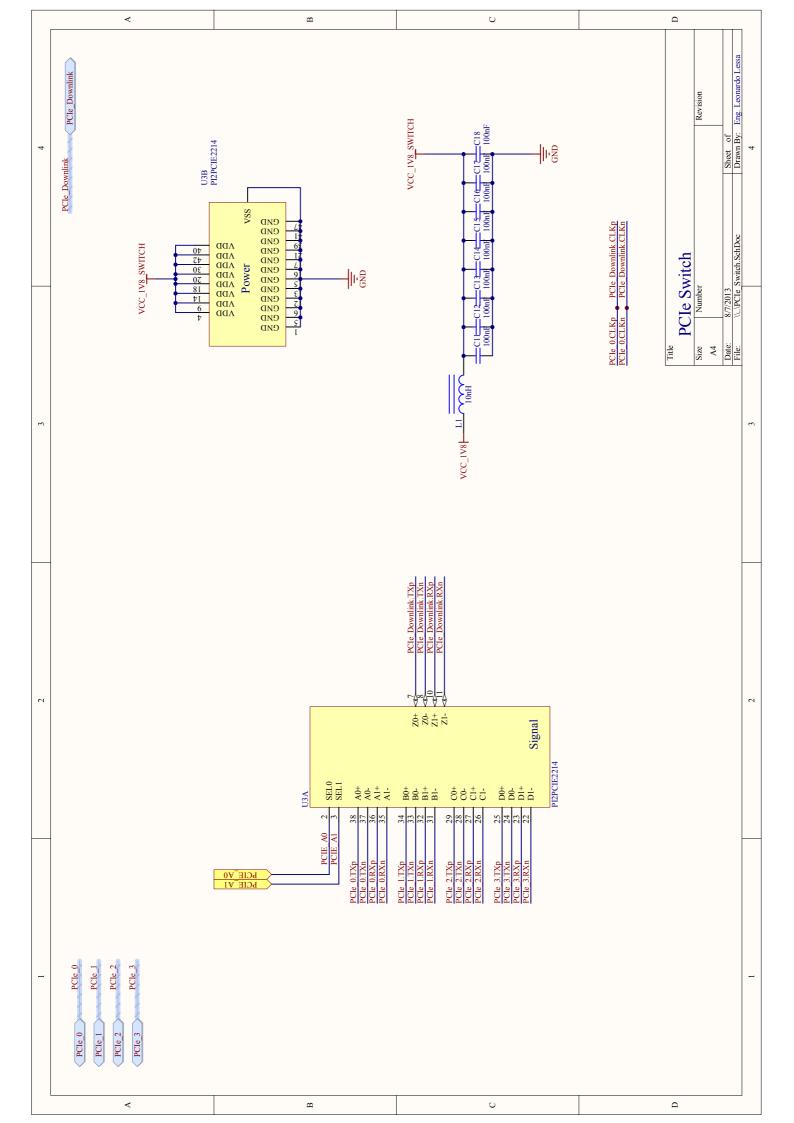

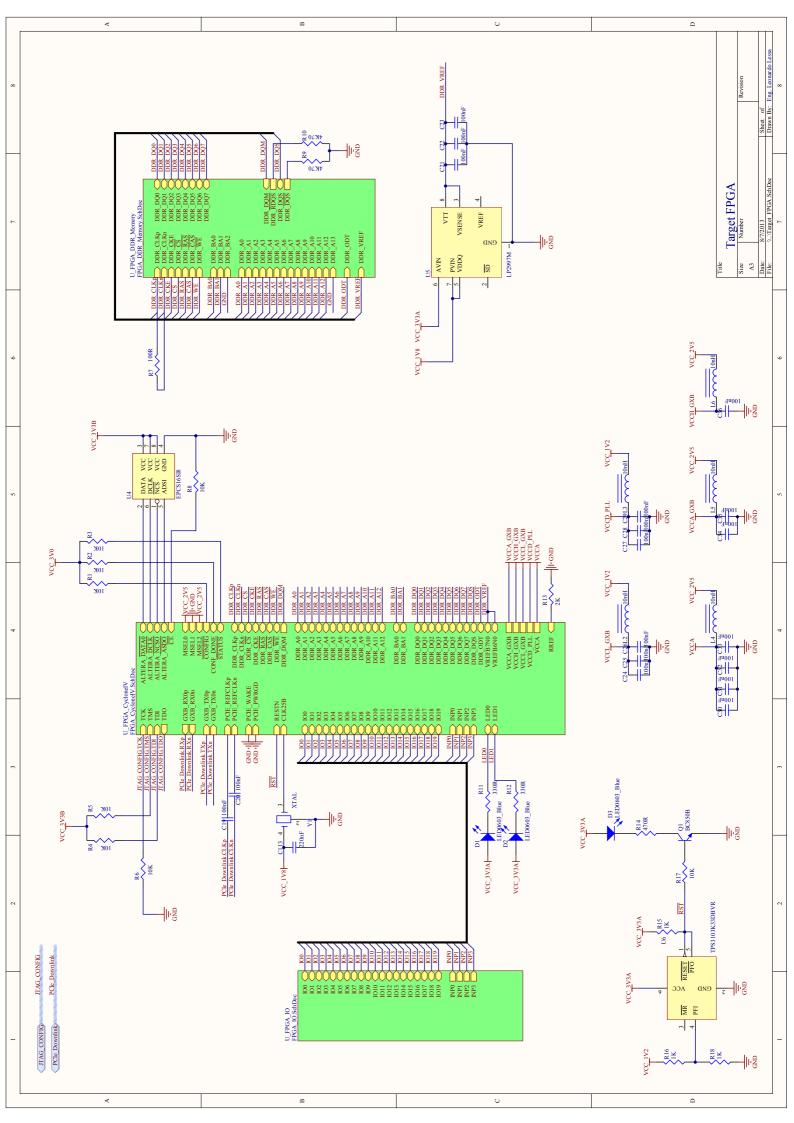

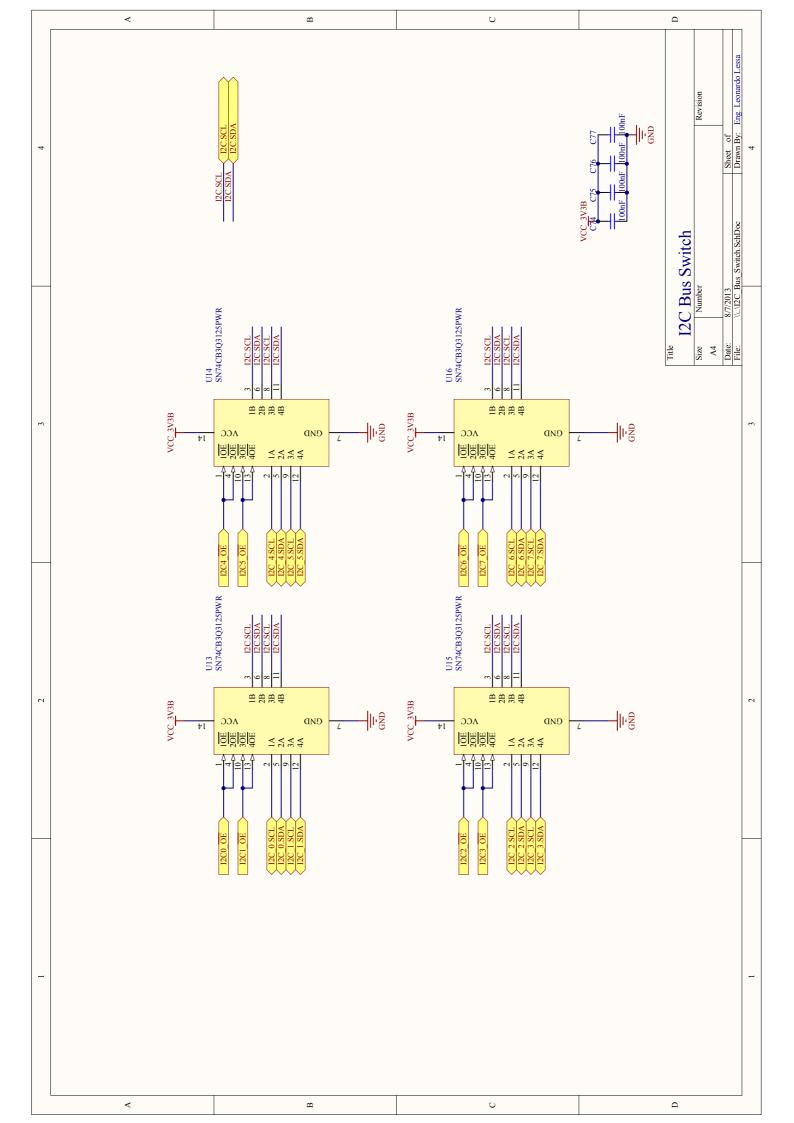

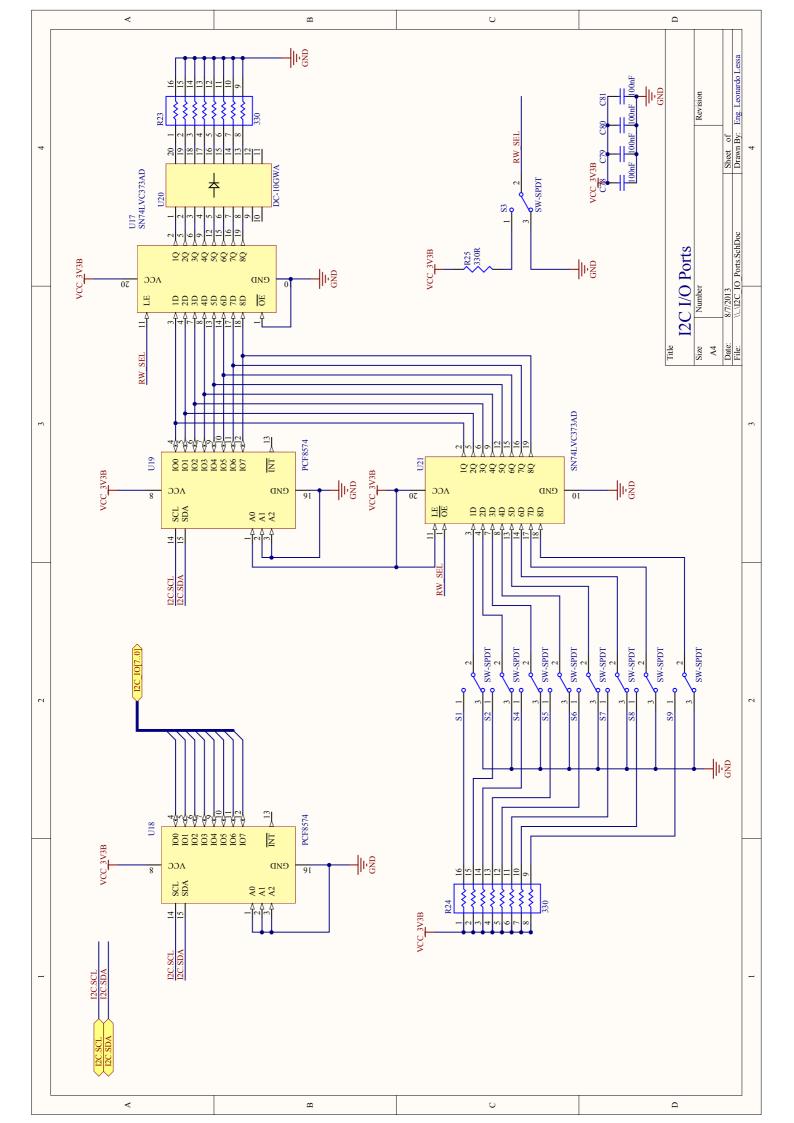

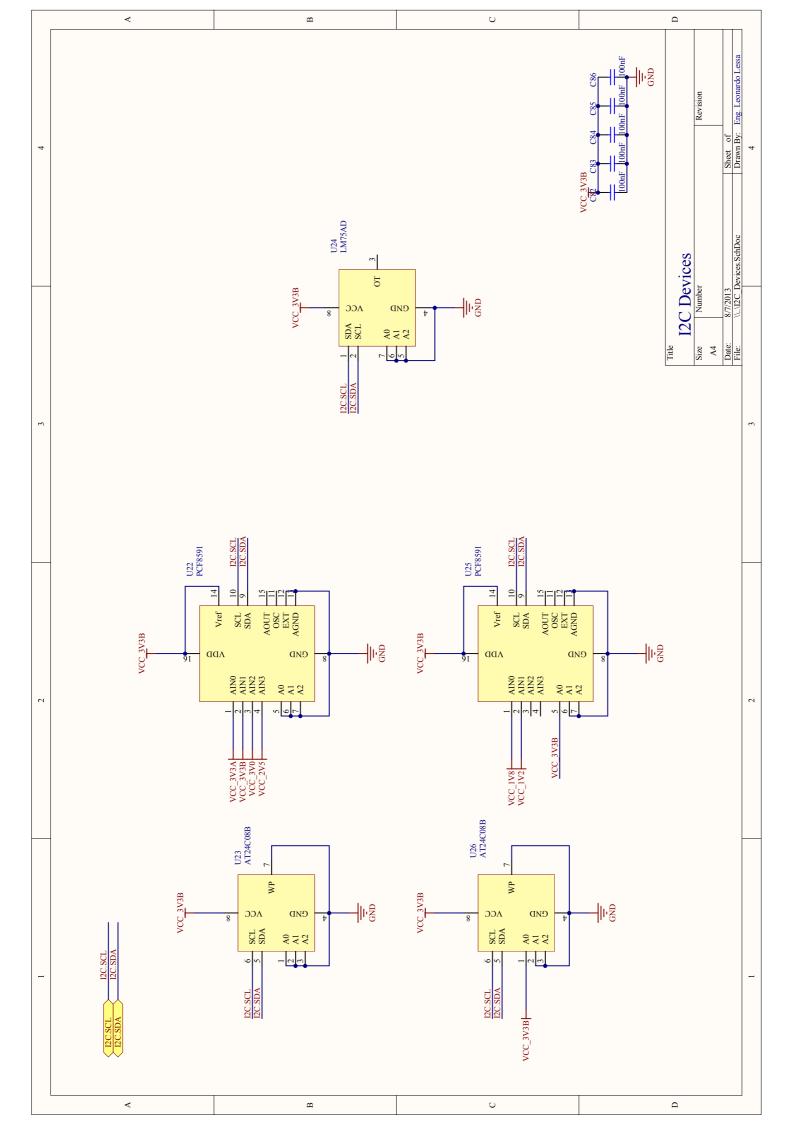

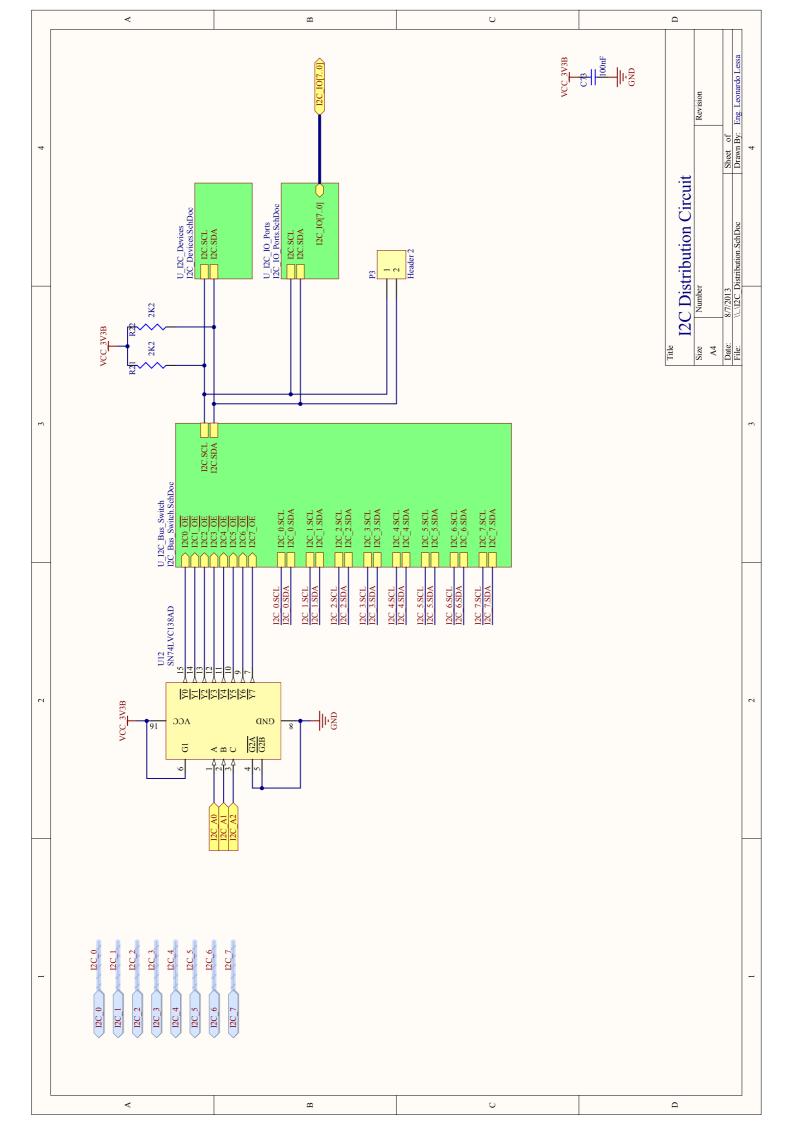

Motivados pela necessidade de upgrade do sistema de controle da placa TELL40, o CBPF desenvolveu um módulo de controle de experimento genérico, ECS-CBPF é uma placa em formato de *mezzanino* que foi projetada para fazer a conexão entre um sistema genérico a ser controlado, chamado neste documento de hospedeiro, e a sala de controle do experimento LHCb através de um link *Gigabit Ethernet*. Consiste em uma unidade de processamento e controle, contendo um CCPC modelo COMe-mTTi10 da Kontron [27] carregada com o sistema operacional Linux, uma unidade lógica programável Cyclone IV (FPGA) que faz o interfaceamento do CCPC com dispositivos de baixa velocidade como I<sup>2</sup>C, JTAG e SPI a serem configurados e monitorados pela sala de controle e um *switch* PCIe PEX8609 da PLX [28] para a comunicação com outras unidades logicas programáveis em alta velocidade utilizando o barramento PCIe. Os componentes do módulo são alimentados por meio de uma tensão externa proveniente do hospedeiro.

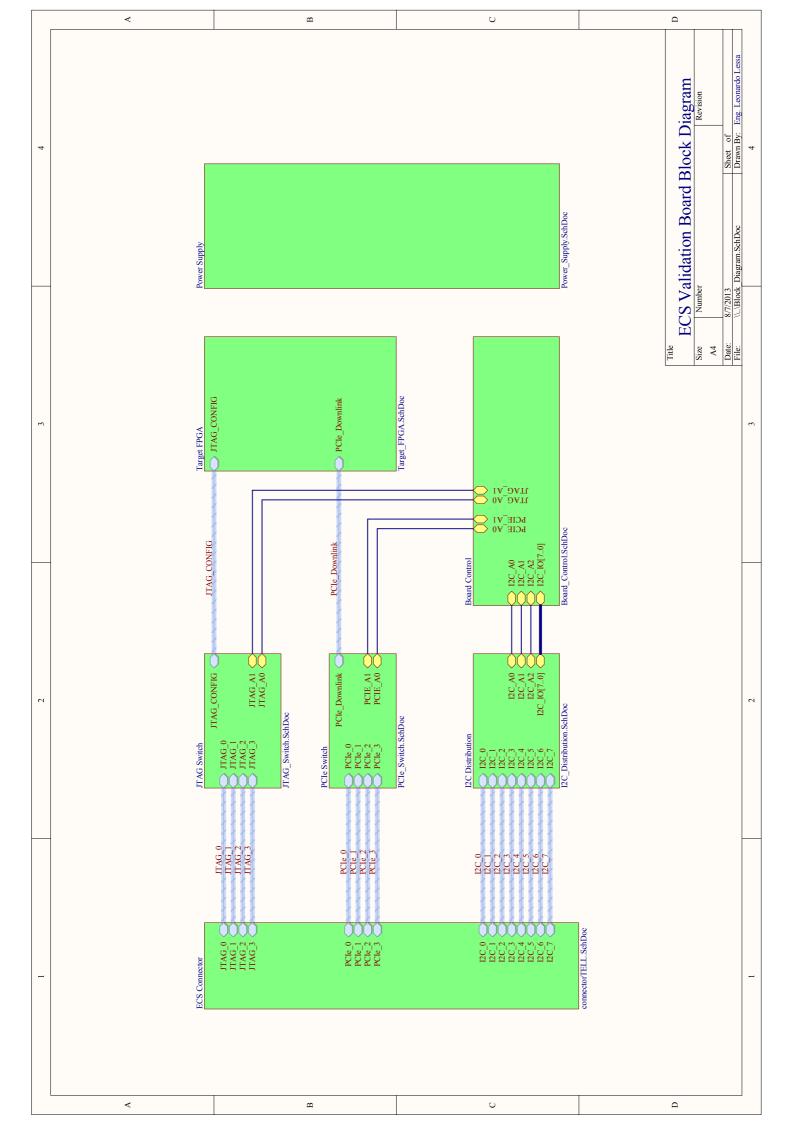

O ECS-CBPF e seu diagrama de blocos são apresentando nas Figuras 24 e 25, respectivamente.

Figura 24 - Módulo Experiment Control System - CCPC CBPF

Figura 25 - Diagrama de blocos do módulo ECS-CBPF

As seguintes funcionalidades são encontradas:

- Computador de controle

- Interface padrão Gigabit Ethernet

- Seis canais de comunicação PCle

- Oito controladores independentes I<sup>2</sup>C

- Quatro controladores independentes JTAG

- 36 pinos de Entradas/Saídas genéricas

## 5.1 Protocolos e barramentos de comunicação

Para que a comunicação entre a sala de controle e a placa de aquisição seja realizada é necessária a criação entre alguns protocolos de comunicação que serão explicados a seguir.

#### 5.1.1 Barramento PCIe

O padrão PCI Express [29] (PCIe) é uma evolução do PCI[30], barramento de comunicação entre um processador (*rootport*) e periféricos (*endpoint*) em um computador. Apesar de não se enquadrar fisicamente como um barramento, uma vez que o mesmo utiliza linhas seriais de transmissão e recepção para a comunicação, por questões históricas referese ao PCIe como um barramento. É importante ressaltar que no ponto de vista de *software* ou *drivers* nos sistemas operacionais o PCIe é totalmente compatível com o PCI.

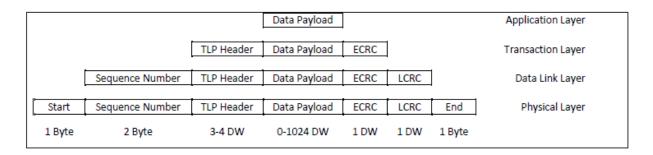

O protocolo de comunicação utilizado pelo padrão PCIe é dividido em camadas[30]: camada de transação, camada de *link* de dados e camada física, como mostrado na Figura 26.

A primeira camada do PCIe é a camada de transação TL (*Transaction Layer*.) Esta interage com o dispositivo PCIe e a camada inferior a ela. A TL é responsável por iniciar o processo de transmissão de dados transformando uma requisição, provenientes de um dispositivo em um pacote de dados TLP (Transaction Layer Packet). O pacote é composto por informações em um cabeçalho que é codificado de tal forma a identificar o tipo de operação a ser realizada, como a quantidade de bytes necessários para o cabeçalho, e opcionalmente por bytes de dados, quando necessário.

A camada de link de dados DLL (*Data Layer Link*) interage com a primeira e terceira camadas. Seu principal objetivo é garantir a integridade dos dados que circulam pelo *link* PCle. Para isto, a DLL adiciona uma sequencia numérica única no inicio do pacote e uma codificação para checagem de erros no final do mesmo. Utiliza-se a técnica de CRC (Checagem de Redundância Cíclica) para detecção de erros. Caso seja detectado um problema a DLL gera um pacote DLLP (*Data Layer Link Packet*) que é transmitido de volta para o dispositivo. Este pacote contém informações específicas, tais como o gerenciamento de hierarquia, notificação de erros, controle de fluxo de dados e outros.

A camada física (PL – *Physical Layer*) do PCIe é responsável pela transmissão e recepção das camadas anteriores através de sinais elétricos, composta por dois pares diferenciais, em geral do tipo LVDS ou PCML. Um par é responsável pela transmissão (TX) e outro pela recepção (RX). Juntos constituem em um *lane*. Pode-se combinar *lanes* em paralelo para se obter um *link*. Um *link* é composto por no mínimo um *lane* (1x), outras configurações disponíveis são: 2x, 4x, 8x, 16x e 32x. No padrão PCIe 1.1 [31] a capacidade de transporte de dados é de 2.5 Gb/s em cada direção, ou seja 250 MB/s de dados brutos (Sem levar em conta o *overhead* de cabeçalhos e outras informações), atingindo um máximo de 80 Gb/s na configuração 32x. A Figura 26 representa um pacote completo PCIe.

Figura 26 - Pacote de dados PCIe

## 5.1.2 Barramento I<sup>2</sup>C

O barramento I<sup>2</sup>C foi desenvolvido em meados dos anos 80 pela Philips, inicialmente concebido para fazer a interconexão entre uma CPU e *chips* controladores em televisores. Percebeu-se que conforme a medida que quantidade de periféricos aumenta em um barramento paralelo, as conexões se tornam mais complexas, aumentando os custos de projeto e desenvolvimento, além de tornar a placa do circuito mais suscetível à interferência eletromagnética (EMI). Por conta destes problemas, adotou-se um barramento serial de dois fios. Atualmente este barramento tornou-se padrão na indústria e fabricantes de semicondutores como Atmel, Intel, Microchip, Maxim, Texas Instrument entre outros, fabricam dispositivos compatíveis com este barramento com as mais diversas funções, como por exemplo memórias, displays, conversores A/D e D/A, sensores de temperatura, pressão e humidade, etc.

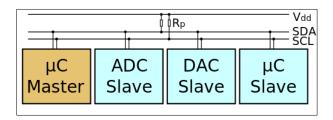

Fisicamente o barramento consiste em duas portas (fios ou linhas de comunicação) de coletor-aberto bidirecionais SDA (*Serial Data Line*) e SCL (*Serial Clock Line*). Os dispositivos são dispostos no barramento em uma arquitetura Mestre/Escravo, onde sempre o Mestre

inicializa uma comunicação. Alguns dispositivos podem atuar, não simultaneamente, como Mestre e Escravo. Como visto na Figura 27.

Figura 27 - Barramento I<sup>2</sup>C

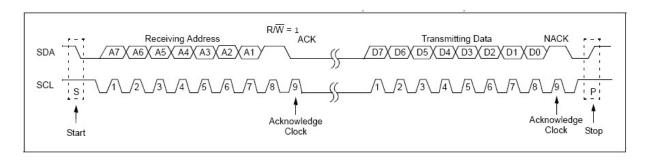

O protocolo de comunicação I<sup>2</sup>C segue o seguinte fluxo:

- O dispositivo Mestre envia ao barramento um sinal START. Isto faz com que os dispositivos Escravos esperem por uma comunicação.

- O dispositivo Mestre envia um registro com o endereço do dispositivo Escravo a ser acessado e a direção da comunicação, leitura ou escrita.

- Se o dispositivo n\u00e3o for o respons\u00e1vel pelo endere\u00f3o, este ir\u00e1 ignorar os comandos e aguardar\u00e1 o sinal de STOP.

- O dispositivo com o endereço solicitado enviará uma resposta com um sinal de ACK (Acknowledge).

- Logo após o dispositivo Mestre receber o sinal de ACK, inicia-se a transmissão ou requisição de dados. Após o termino das operações o Mestre envia o sinal de STOP e libera o barramento para outro Mestre atuar.

O processo descrito no fluxo à cima pode ser observado na Figura 28.

Figura 28 - Protocolo I<sup>2</sup>C

Os sinais de *clock* são gerados pelos dispositivos Mestres através da linha SCL e os dados são validos apenas quando o sinal SCL estiver em nível alto.

## 5.1.3 JTAG

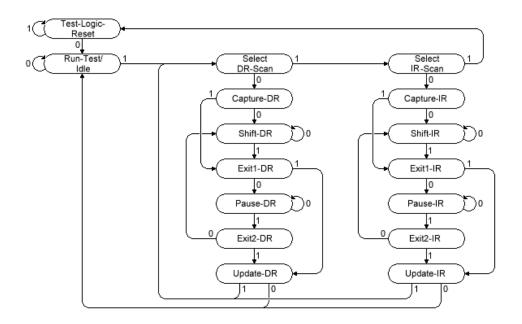

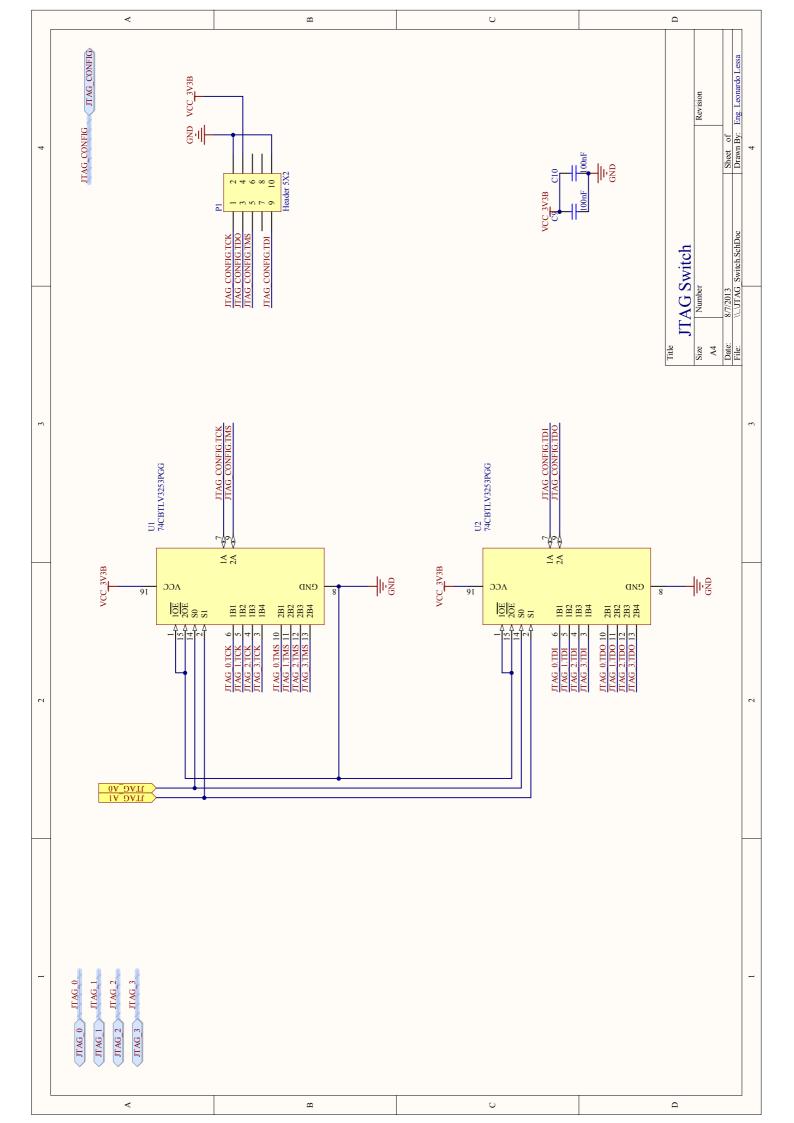

Devido à miniaturização e discretização dos componentes eletrônicos na forma de circuitos integrados e placas de circuitos impressos com diversas camadas, acrescentou-se certa dificuldade para a realização dos testes através de pontas de prova na superfície destes circuitos. Em 1985 foi criado um grupo internacional (JTAG – *Joint Action Group*) para o desenvolvimento de uma solução deste problema. Após alguns anos de sua criação, esta solução foi adotada por grande parte da indústria e assim criou-se o padrão IEEE Std. 1149.1-1990: IEEE *Standatd Test Access Port and Boundary Scan Architecture*[32], também conhecido como JTAG. Este padrão utiliza componentes em *hardware* nos circuitos integrados, permitindo o controle através de *software*. Recentemente o grupo JTAG, desenvolveu e publicou um novo padrão o IEEE Std 1532.2-2010: *IEEE Standard for System Configuration of Programmable Devices* [33] e seu objetivo foi padronizar a configuração de dispositivos lógicos programáveis, as FPGA, através da interface JTAG.

A interface JTAG é composta por quatro pinos (um quinto opcional) e um conjunto de registradores de controle e de dados. Seu objetivo é permitir a realização de testes e monitoramento de níveis lógicos nos pinos de um circuito integrado que contém esta interface. Para selecionar o tipo de teste executado pela interface utiliza-se o *Instruction Register* (IR), o qual realiza monitoramento do nível de lógica do circuito o *Boundary Scan Register* (BSR) conectado diretamente a cada pino do dispositivo. Em conjunto com IR existe o *Data Register* (DR), para instruções de recebimento e envio de dados.

#### Os pinos existentes são:

- TCK: Sinal de Clock.

- TMS: Seleção do modo de teste (*Test Mode Select*).

- TDI: Entrada de dados.

- TDO: Saída de dados.

- TRST: Sinal de *Reset* (Opcional).

O Sinal TMS controla uma máquina de estado, chamada de *Test Access Port* (TAP), responsável pela execução dos testes e fluxo de dados do dispositivo. A Figura 29 ilustra o diagrama da máquina de estado do controlador TAP.

Figura 29 - Máquina de estado do controlador JTAG

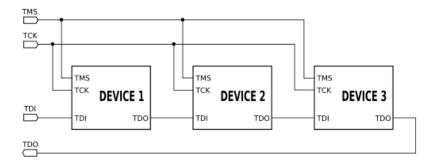

O gerenciamento dos sinais, controle dos testes e configuração dos dispositivos que possuem uma interface JTAG, é realizado pelo controlador JTAG *master*, que pode controlar um ou mais dispositivos ligados em cadeia, como mostrado na Figura 30.

Figura 30 - Configuração de uma chain JTAG

## 5.2 Ferramentas de desenvolvimento

O projeto ECS-CCPC ECS foi desenvolvido utilizando ferramentas comerciais disponíveis, são elas:

- Kit de desenvolvimento PCle Cyclone IV (DB4CGX15) [34] em conjunto com o programa da Altera, Quartus II [35], e seus módulos.

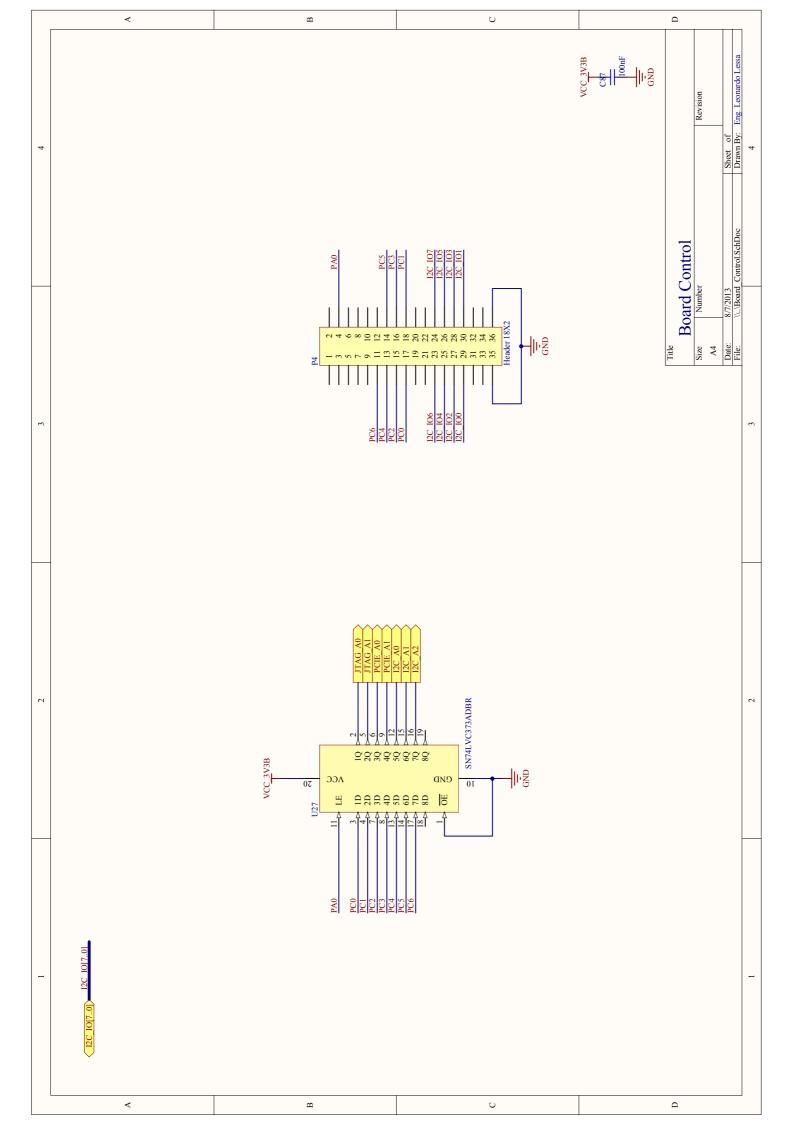

- O programa Altium Design Summer 09 [36], Utilizado para o desenho do esquemático (Apêndice A) da placa e confecção de layout para posterior produção da placa.

## 5.3 Kit de desenvolvimento Cyclone IV (DB4CGX15)

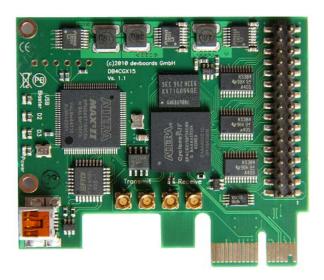

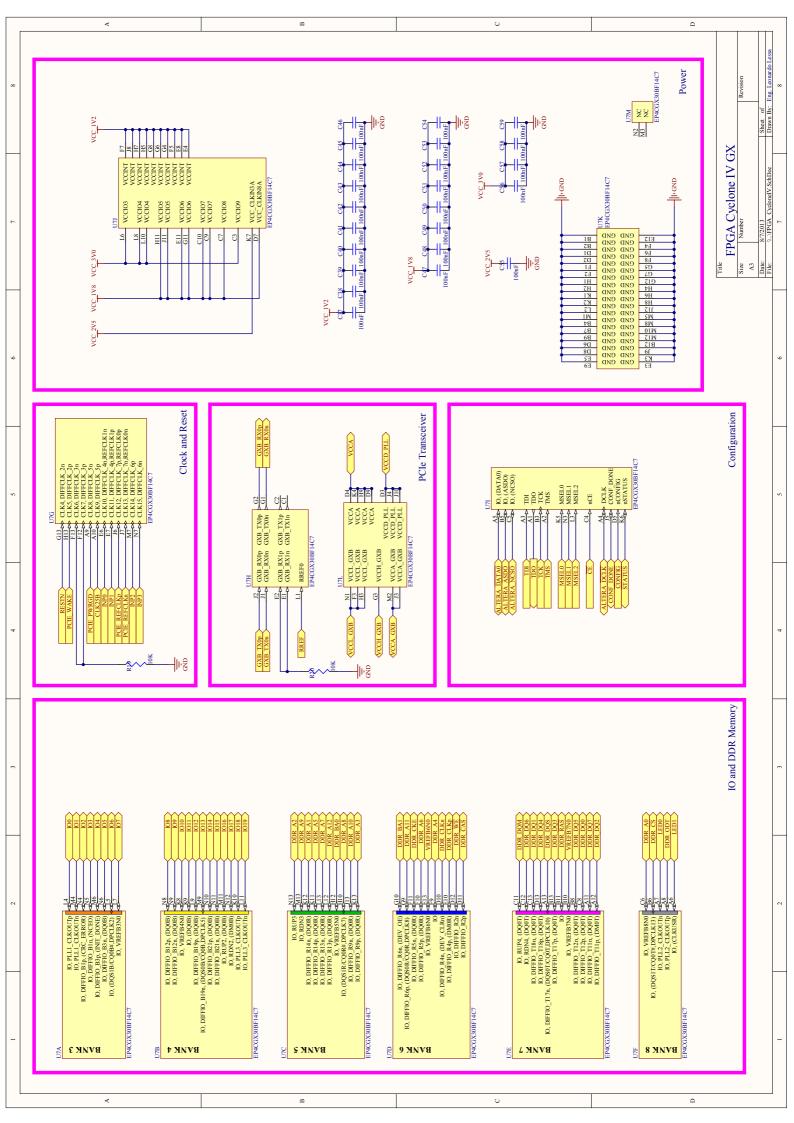

O kit de desenvolvimento DB4CGX15, mostrado na Figura 31, utiliza um FPGA da família Cyclone IV (EP4CGX15C6N), de baixo custo e consumo se comparado com outras famílias do mesmo fabricante. Possui um bloco em hardware dedicado para o protocolo PCIe possibilitando assim um maior desempenho e economia em relação a recursos utilizados dos elementos lógicos disponíveis no FPGA. No modelo utilizado pelo kit encontram-se disponíveis 15.000 elementos lógicos para o desenvolvimento de aplicações além de um chip de configuração (EPCS16), memória do tipo DDR2 (256MB), programador USB integrado e um conector com pinos de Entrada/Saída.

Figura 31 - Kit de desenvolvimento DB4CGX15

Com a utilização deste kit foi possível projetar e verificar o funcionamento do protocolo PCIe, assim como a conexão com os outros controladores encontrados no projeto a serem descritos no tópico do desenvolvimento do *firmware*, antes mesmo do desenvolvimento da placa.

Baseado no desenvolvimento utilizando o kit foi possível estimar a utilização de recursos no FPGA possibilitando assim à escolha do chip adequado as características do ECS-CBPF.

## 5.4 Desenvolvimento do Hardware

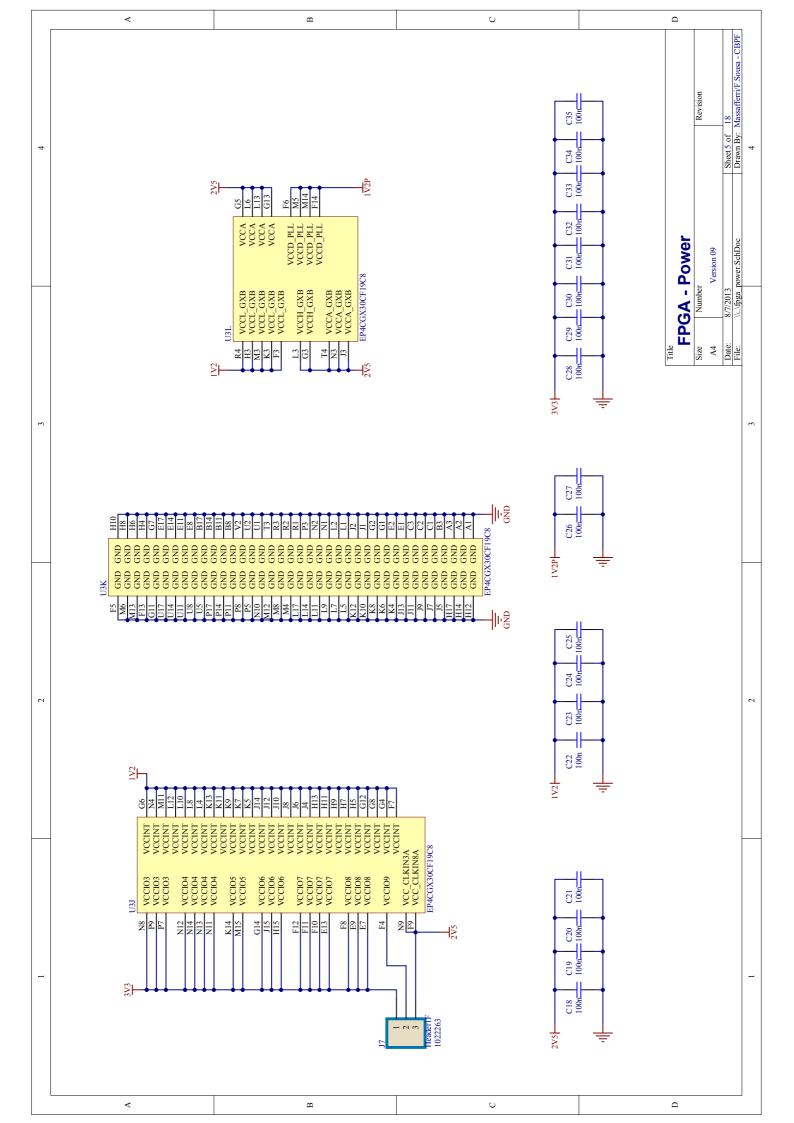

## 5.4.1 Distribuição de alimentação

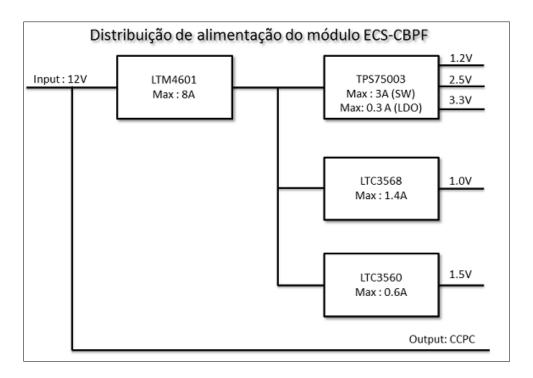

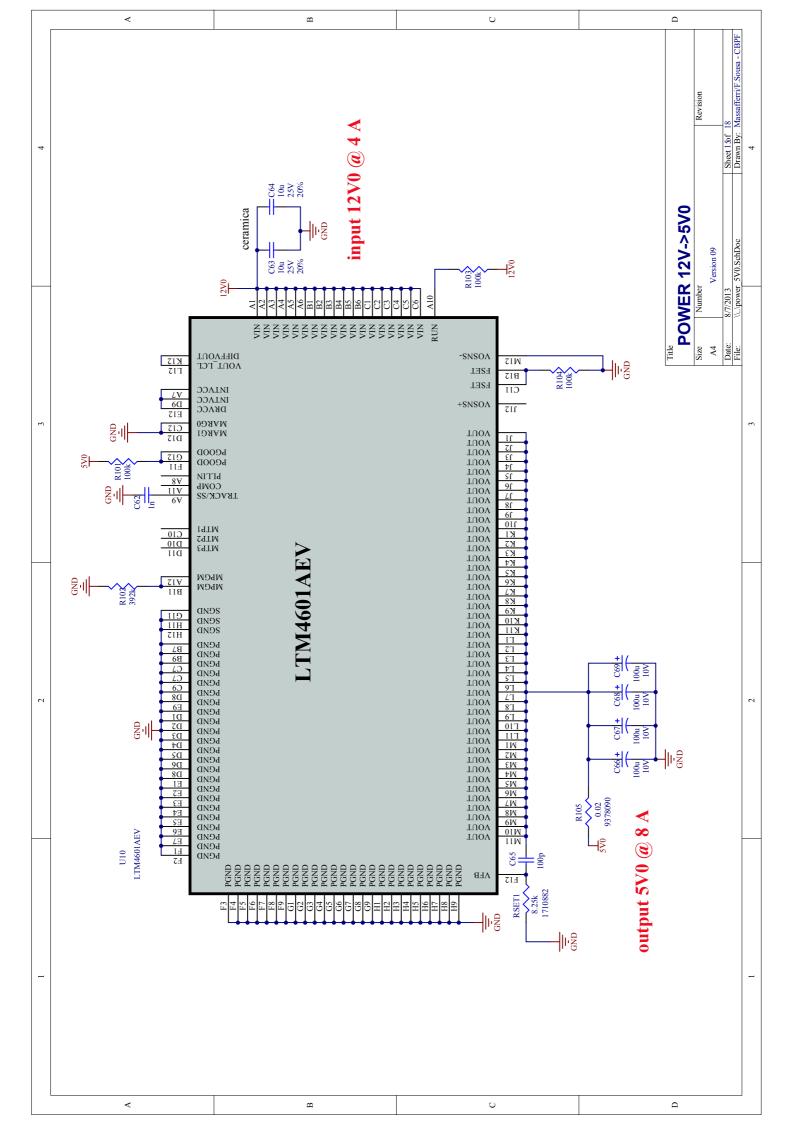

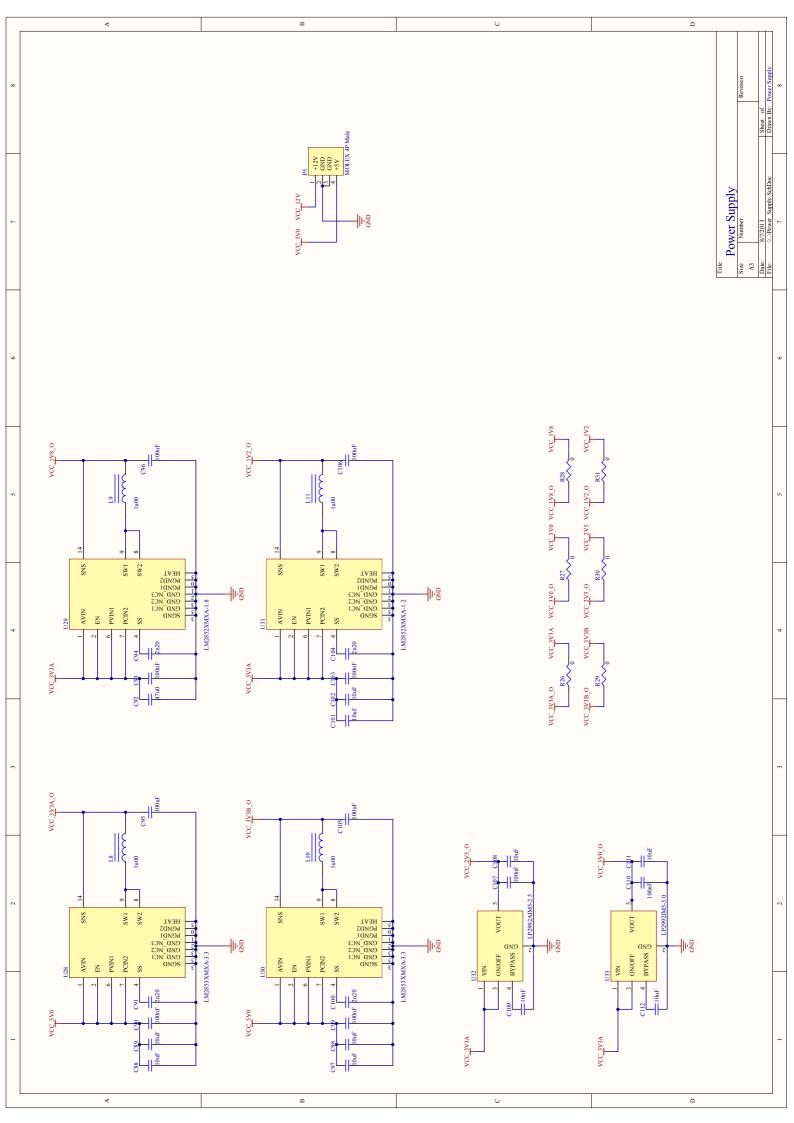

O módulo recebe como entrada do sistema hospedeiro a tensão de alimentação de 12V e gera todas as tensões necessárias para seu funcionamento. A Figura 32 mostra a representação da distribuição das tensões envolvidas no projeto.

Figura 32 - Distribuição da alimentação do módulo ECS

No primeiro estágio a tensão de entrada é diretamente conectada ao CCPC e ao regulador LTM4601[37] . Este gera 5 V o qual é convertido em tensões mais baixas através de dois reguladores; o primeiro LTC3568[38] fornece a tensão de 1.0 V, e TPS75003[39] fornece as tensões de 1.2 V, 2.5 V e 3.3 V.

## 5.4.2 Distribuição de Clock

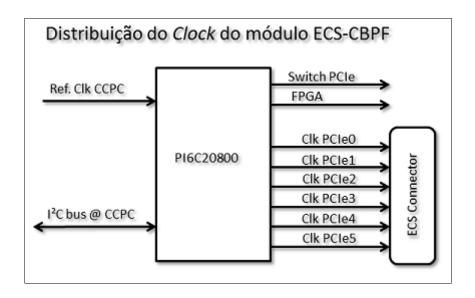

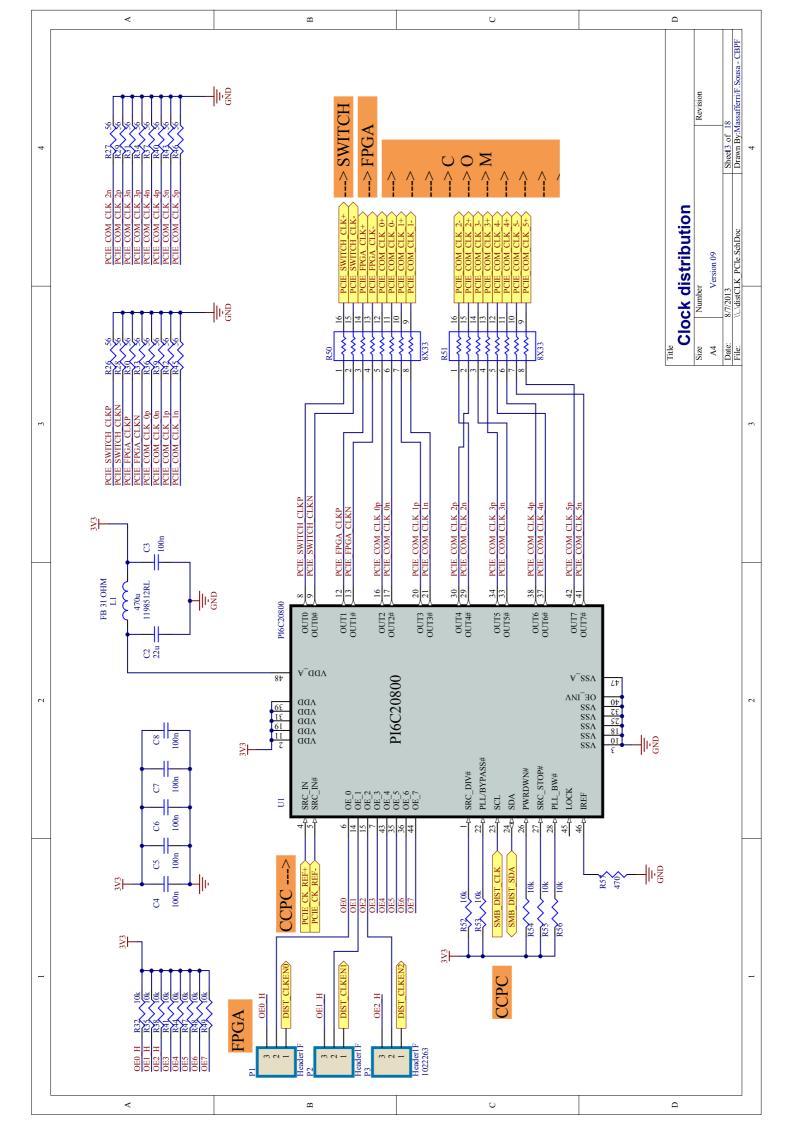

Para que todos as seis saídas PCIe fornecidas pelo *switch PCIe* estejam disponíveis é necessário que o *clock* de referência do PCIe seja distribuído. Para este fim utiliza-se o circuito PI6C20800[40] como mostra a Figura 33.

Figura 33 - Distribuição de clock de referência PCIe

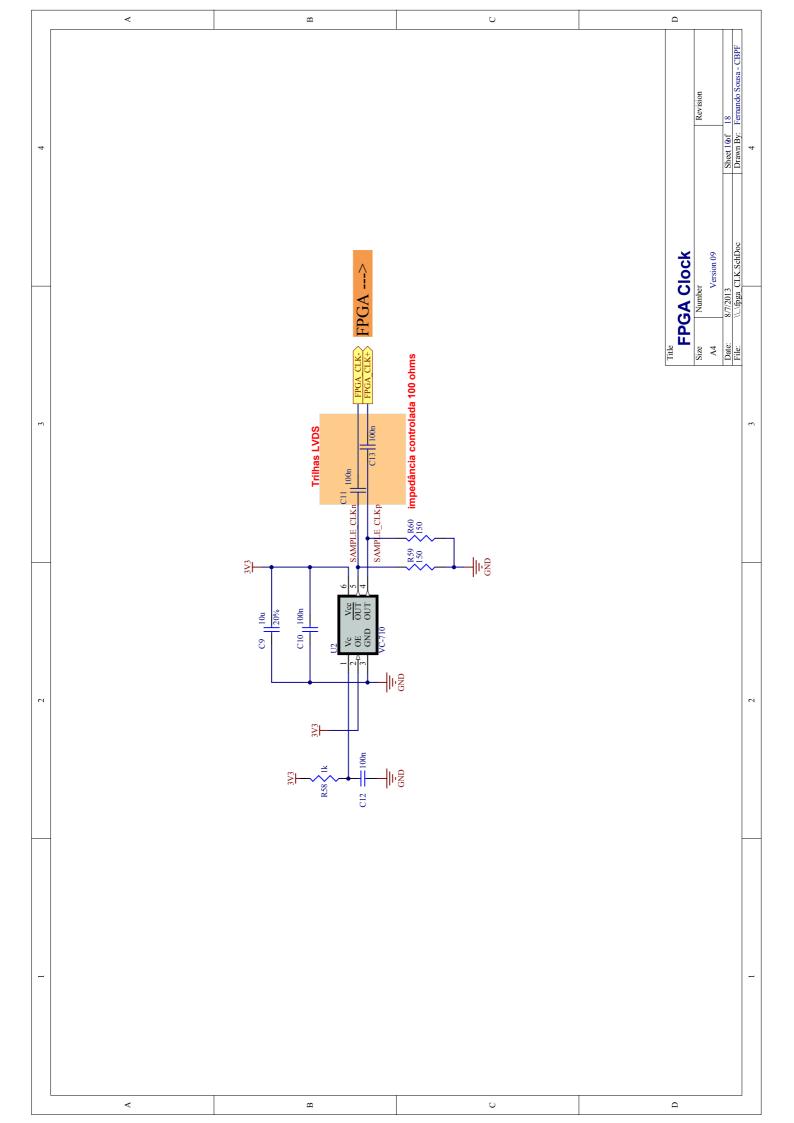

Um circuito oscilador a cristal de 125 Mhz do tipo LVPECL é conectado diretamente ao FPGA e utilizado como referência dos componentes internos do FPGA.

## 5.4.3 CCPC

O CCPC é um módulo do tipo COM Express R2.0 com conector Type 10[41] encontrado comercialmente e fabricado por diversas empresas. O módulo possui um circuito altamente integrado com baixo consumo de energia e são compostos por uma unidade de processamento (CPU) e memória, além de dispositivos de I/O encontrados em um computador comum, como USB, áudio, gráfico e rede. Todos os sinais de I/O são mapeados em um conector de alta densidade e podem ser utilizados em circuitos específicos. A escolha de um sistema padronizado proporciona a fácil substituição caso seja necessário o aumento do desempenho em sistemas futuros.

O módulo COM Express utilizado neste projeto é o nanoETXexpressTTi 1.0Ghz 512/mSD da empresa Kontron e pode ser visto na Figura 34.

Figura 34 - Módulo CCPC Kontron

#### Este módulo possui:

- Um processador Intel Atom E640T (1 Ghz).

- Até 3Gb de memória RAM DDR onboard.

- Quatro linhas PCIe, uma reservada para conexão com o controlador de sistema (Southbridge).