### CENTRO BRASILEIRO DE PESQUISAS FÍSICAS

LAFEX - LABORATÓRIO DE FÍSICA EXPERIMENTAL

# Desenvolvimento de Sistema de Controle para Eletrônica de Front-End do Detector de Fibras Cintilantes do LHCb

Maurício Féo Pereira Rivello de Carvalho

Dissertação de mestrado apresentada ao Centro Brasileiro de Pesquisas Físicas como parte dos requisitos necessários à obtenção do título de Mestre em Física.

Orientador: Prof. Dr. André Massafferri Rodrigues

Rio de Janeiro - RJ

Maio, 2016

### Agradecimentos

À Raquel, meu incentivo, minha alegria, minha vida.

Aos meus pais, Osvaldo e Laís e meus sogros, Delio e Ermitas, que foram o meu suporte durante este período.

Ao meu orientador, André Massafferri, por todas as oportunidades e a confiança depositada em mim.

Ao Antonio Pellegrino, por proporcionar a continuação deste caminho.

Ao Federico Alessio, pela supervisão e orientação.

Aos meus colegas Leonardo Guedes e Cairo Caplan, por ter tornado esta jornada divertida.

A todos os que colaboraram direta ou indiretamente para esta realização.

#### Resumo

O experimento LHCb está se preparando para seu upgrade, que envolverá a troca de seu sistema de aquisição de dados e de grande parte de seus detectores e eletrônica adjacente.

O CBPF se insere neste contexto como o responsável pelo desenvolvimento de um sistema de teste para validação dos módulos eletrônicos e módulos de fibras cintilantes antes da fase de transporte e montagem do detector na área experimental subterrânea.

O presente projeto se caracteriza pela validação do módulo eletrônico MiniDAQ para ser utilizado como plataforma de aquisição de dados no sistema de teste, e o desenvolvimento de um sistema supervisório de controle e monitoramento para o sistema citado, cujo objetivo é configurar e monitorar todos os dispositivos da eletrônica de front-end a ser testada assim como os demais componentes do sistema, fornecendo painéis virtuais criados no software SCADA WinCC para possibilitar a criação de rotinas de teste para o futuro detector.

#### Abstract

The LHCb experiment is preparing for it's upgrade, which will involve the replacement of it's data acquisition system and most of its adjacent detectors and electronics.

The CBPF is inserted in this context as the responsible for the development of a test system for validation of electronic modules and scintillating fiber modules before the phase of shipping and assembly of the detector in the underground experimental area.

This project is characterized by the validation of the electronic module MiniDAQ to be used as a data acquisition platform in the test system, and the development of a supervisory monitoring and control system for the said platform, whose aim is to set up and monitor all devices electronic front-end to be tested as well as other system components, providing virtual panels created in the WinCC SCADA software to allow the creation of test routines for the future detector.

# Sumário

| 1 | Intr                                            | rodução                                      | 1  |  |  |

|---|-------------------------------------------------|----------------------------------------------|----|--|--|

| 2 | O Grande Colisor de Hádrons e seus Experimentos |                                              |    |  |  |

| 3 | O Experimento LHCb                              |                                              |    |  |  |

|   | 3.1                                             | VeLo                                         | 10 |  |  |

|   | 3.2                                             | Magneto                                      | 11 |  |  |

|   | 3.3                                             | Sistema de Trajetografia                     | 12 |  |  |

|   | 3.4                                             | RICH                                         | 14 |  |  |

|   | 3.5                                             | Calorímetro                                  | 15 |  |  |

|   | 3.6                                             | Sistema de Múons                             | 16 |  |  |

|   | 3.7                                             | Trigger                                      | 17 |  |  |

|   | 3.8                                             | Sistema Online                               | 18 |  |  |

| 4 | Upgrade do LHCb                                 |                                              |    |  |  |

|   | 4.1                                             | GBT                                          | 23 |  |  |

|   | 4.2                                             | Trigger e DAQ                                | 26 |  |  |

|   | 4.3                                             | Upgrade dos Detectores Inner e Outer Tracker | 28 |  |  |

| 5 | O Detector de Fibras Cintilantes                |                                              |    |  |  |

|   | 5.1                                             | Composição de um Módulo do Detector          | 32 |  |  |

|   | 5.2                                             | As Fibras Cintilantes                        | 34 |  |  |

|   | 5.3                                             | Módulos de Leitura                           | 34 |  |  |

|   | 5.4                                             | Fotomultiplicadoras de Silício               | 35 |  |  |

| 6 | Eletrônica de Front-End do SciFi                       |                                                |    |  |  |  |  |  |

|---|--------------------------------------------------------|------------------------------------------------|----|--|--|--|--|--|

|   | 6.1                                                    | Pacific Board e o Chip PACIFIC                 | 41 |  |  |  |  |  |

|   | 6.2                                                    | 2 Clusterization Board                         |    |  |  |  |  |  |

|   | 6.3                                                    | Master Board                                   | 45 |  |  |  |  |  |

|   | 6.4                                                    | Caminho de Dados Alternativo                   | 46 |  |  |  |  |  |

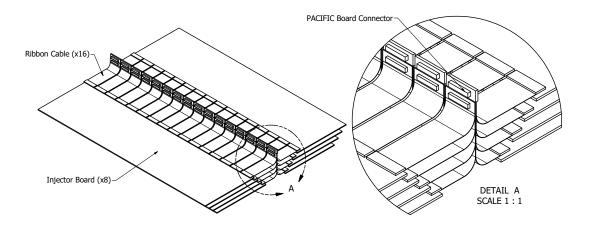

| 7 | Sist                                                   | Sistema de Teste da Eletrônica do SciFi        |    |  |  |  |  |  |

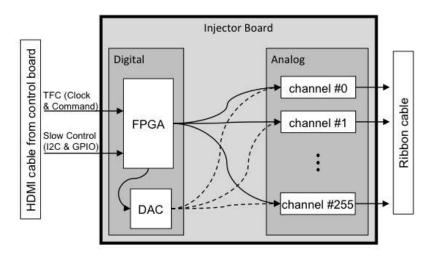

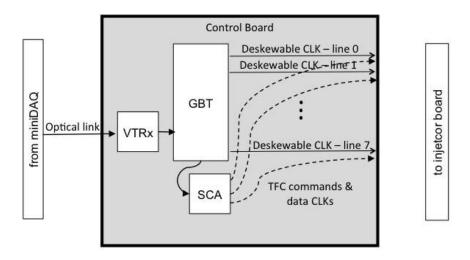

|   | 7.1                                                    | Placa de Controle do Sistema de Injeção        | 50 |  |  |  |  |  |

|   | 7.2                                                    | Placa Injetora do Sistema de Injeção           | 51 |  |  |  |  |  |

|   | 7.3                                                    | Protótipo da Placa Injetora                    | 54 |  |  |  |  |  |

| 8 | MiniDAQ 5                                              |                                                |    |  |  |  |  |  |

|   | 8.1                                                    | AMC40                                          | 57 |  |  |  |  |  |

|   |                                                        | 8.1.1 Firmware do MiniDAQ                      | 59 |  |  |  |  |  |

|   | 8.2                                                    | CCPC                                           | 62 |  |  |  |  |  |

|   |                                                        | 8.2.1 Boot do CCPC                             | 63 |  |  |  |  |  |

|   |                                                        | 8.2.2 Máquina Virtual para Boot do CCPC        | 64 |  |  |  |  |  |

|   | 8.3                                                    | Validação e Depuração do MiniDAQ               | 66 |  |  |  |  |  |

|   |                                                        | 8.3.1 Teste da Camada Física                   | 66 |  |  |  |  |  |

|   |                                                        | 8.3.2 Configuração de Software do CCPC         | 67 |  |  |  |  |  |

|   |                                                        | 8.3.3 Interface entre o CCPC e o FPGA da AMC40 | 69 |  |  |  |  |  |

|   |                                                        | 8.3.4 Loopback                                 | 71 |  |  |  |  |  |

|   |                                                        | 8.3.5 Firmware de Raw Data                     | 74 |  |  |  |  |  |

|   |                                                        | 8.3.6 Firmware GBT simplificado em Stratix IV  | 75 |  |  |  |  |  |

|   |                                                        | 8.3.7 Testando o MiniDAQ com um chip GBT Real  | 76 |  |  |  |  |  |

| 9 | Desenvolvimento do Sistema de Controle da FEE do SciFi |                                                |    |  |  |  |  |  |

|   | 9.1                                                    | Sistema de Controle                            |    |  |  |  |  |  |

|   | 9.2                                                    | Estrutura básica de um sistema WinCC           |    |  |  |  |  |  |

|   | 9.3                                                    | Cadeia de dados do sistema de controle         | 86 |  |  |  |  |  |

|   | 9.4                                                    | Utilização da placa VLDB para desenvolvimento  |    |  |  |  |  |  |

|   | 9.5                                                    | Camada de Software                             |    |  |  |  |  |  |

|               | 9.6                                                                      | Bloco SOL40_SCA do firmware do MiniDAQ                 |                                                                  |     |  |  |  |  |

|---------------|--------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|-----|--|--|--|--|

|               | 9.7                                                                      | Datapoints para descrição da Front-End do SciFi        |                                                                  |     |  |  |  |  |

|               | 9.8                                                                      | .8 Biblioteca de controle fwlbSCIFI                    |                                                                  |     |  |  |  |  |

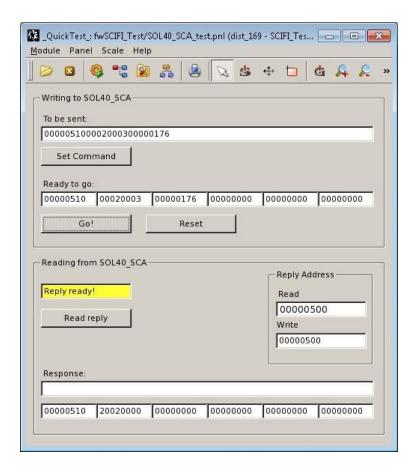

|               |                                                                          | 9.8.1                                                  | Funções de acesso direto ao bloco SOL40_SCA                      | 102 |  |  |  |  |

|               |                                                                          | 9.8.2                                                  | Funções de envio de comandos à eletrônica de $\emph{front-end.}$ | 104 |  |  |  |  |

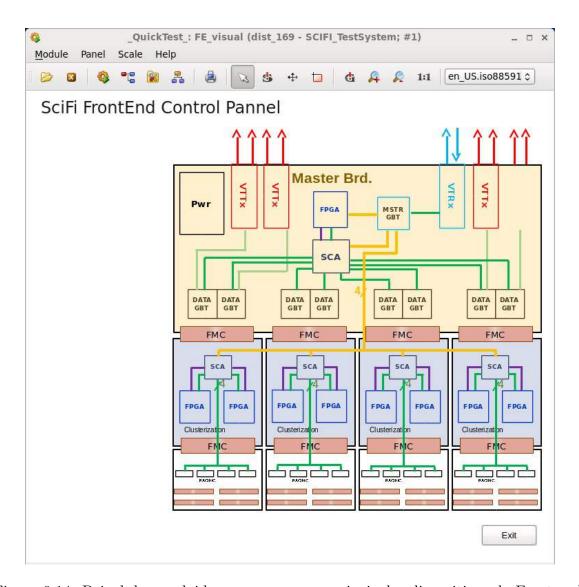

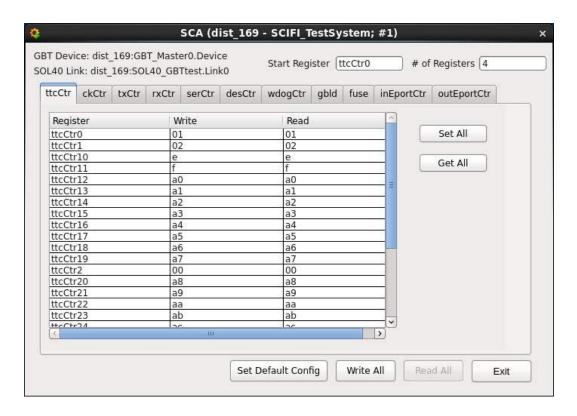

|               | 9.9                                                                      | Painéis de controle para a FE                          |                                                                  |     |  |  |  |  |

|               | 9.10                                                                     | 9.10 Configuração inicial do GBT utilizando um Arduino |                                                                  |     |  |  |  |  |

| 10 Resultados |                                                                          |                                                        |                                                                  |     |  |  |  |  |

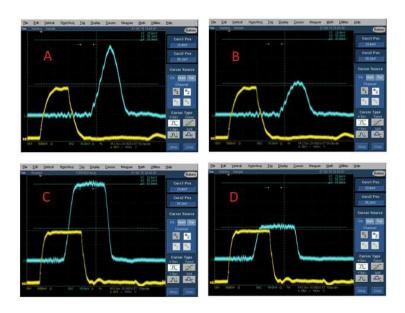

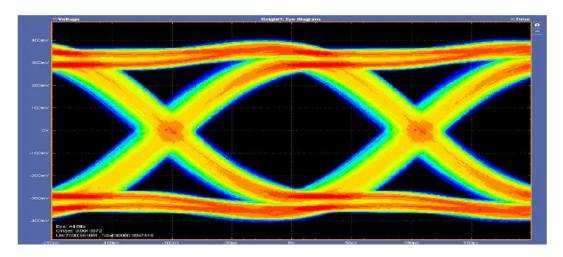

|               | 10.1                                                                     | Sinal ć                                                | óptico do MiniDAQ                                                | 115 |  |  |  |  |

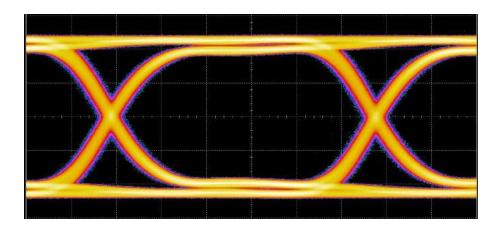

|               |                                                                          | 10.1.1                                                 | Medida com osciloscópio de 4GHz                                  | 115 |  |  |  |  |

|               |                                                                          | 10.1.2                                                 | Medida alternativa com osciloscópio de 20GHz                     | 116 |  |  |  |  |

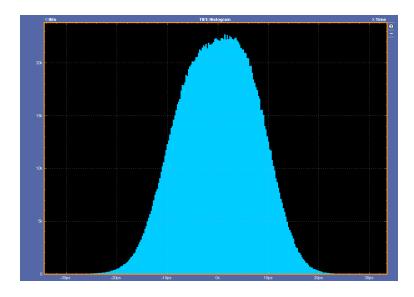

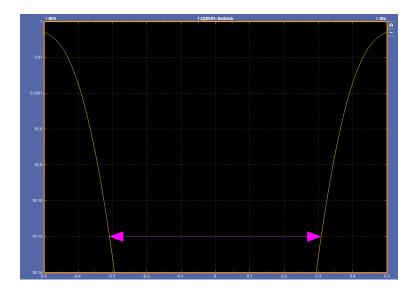

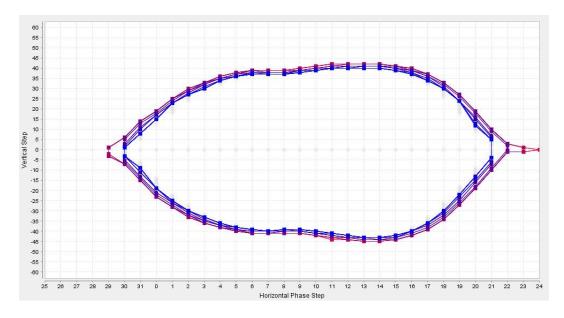

|               |                                                                          | 10.1.3                                                 | Validação do Sinal com o Altera Transceiver Toolkit              | 117 |  |  |  |  |

|               | 10.2                                                                     | Bibliot                                                | teca e Painéis WinCC                                             | 119 |  |  |  |  |

| 11            | Con                                                                      | clusão                                                 |                                                                  | 120 |  |  |  |  |

| Αŗ            | Appendices                                                               |                                                        |                                                                  |     |  |  |  |  |

| A             | A Código da Biblioteca fwlbSCIFI                                         |                                                        |                                                                  |     |  |  |  |  |

| В             | B Firmware do Conversor USB-I2C para Arduino                             |                                                        |                                                                  |     |  |  |  |  |

| $\mathbf{C}$  | Histórico de Modificações Desde a Criação da Máquina Virtual de Boot 14' |                                                        |                                                                  |     |  |  |  |  |

# Capítulo 1

# Introdução

O "Large Hadron Collider" (LHC) é um acelerador de partículas, de 27km de perímetro, projetado para colidir prótons a uma energia de 14TeV e luminosidade de  $10^{34}cm^{-2}s^{-1}$ . Tendo iniciado sua operação no ano de 2009 até sua primeira interrupção programada de 2013 a 2015, os experimentos do LHC acumularam dados suficientes para, em análise posterior, possibilitar importantes descobertas como a do Bóson de Higgs (2012), do decaimento  $B_s^0 \to \mu^+\mu^-$  (2012) e do pentaquark (2015). Operado pela Organização Europeia para Pesquisa Nuclear (CERN), o LHC já está novamente em operação. No entanto, o CERN já trabalha no próximo upgrade do acelerador, a ser instalado na próxima interrupção técnica de 2019 a 2020, e que proporcionará um aumento na sua luminosidade de 5 a 10 vezes a original.

O aumento da luminosidade provocada pelo upgrade do LHC trará consequências aos experimentos. O nível de radiação incidente se tornará substancialmente maior, exigindo a revalidação de todos os componentes localizados nas áreas expostas à radiação das colisões. O volume de dados produzidos também será significantemente maior. O projeto GBT visa oferecer uma solução comum aos problemas citados para todos os experimento. Este fornece um conjunto de componentes para estabelecer links ópticos que transmitam dados a uma taxa de 4.7GBps e que sejam resistentes a radiação.

O experimento "Large Hadron Collider beauty" (LHCb) também sofrerá upgrades para se adequar ao novo regime de luminosidade do LHC. O nível de ocupação no detector Outer Tracker, do sistema de trajetografia, se elevará além do máximo que o algoritmo de reconstrução de trajetórias suporta, exigindo a substituição completa deste detector por um de melhor resolução. Decidiu-se pela substituição completa das estações de trajetória

T1, T2 e T3 por um novo detector a base de fibras cintilantes (SciFi). Com o novo detector, também foi necessário desenvolver nova eletrônica de *front-end*.

Para lidar com o grande volume de dados, foi decidido que será substituída toda a eletrônica de aquisição do experimento, que registra eventos a uma taxa de no máximo 1.1MHz, por uma que fosse capaz de registrar todos os eventos gerados, à taxa de 40MHz que ocorrem os eventos. O sistema de trigger, que era composto por um trigger a nível de hardware (trigger de nível 0) para filtrar os eventos lidos pela eletrônica de aquisição, e um trigger a nível de software (trigger de alto nível) também foi reformulado. O trigger de nível 0 foi completamente extinto, uma vez que todo evento seria enviado para aquisição.

Inicialmente se escolheu utilizar uma arquitetura semelhante ao módulo atual do experimento, chamado de TELL1, em que haveria um módulo mãe com 4 conectores AMC onde seriam inseridos mezaninos. Estes mezaninos, chamados de TELL40, poderiam ser utilizados para aquisição de dados ou para controle, dependendo do firmware utilizado no FPGA. Eles possuem links GBTs e são capazes de fazer a aquisição a 40MHz. Os módulos TELL40 foram desenvolvidos e algumas unidades foram produzidas e distribuídas em um kit para desenvolvimento chamado MiniDAQ.

Posteriormente foi decidido se utilizar uma arquitetura diferente no experimento, e a idéia da TELL40 foi substituída pela PCIe40. Estas placas consistem em módulos semelhantes à TELL40 mas que se conectam diretamente aos computadores de aquisição de dados, através de uma interface PCIexpress. No entanto, para algumas aplicações que não tem os mesmos requisitos do experimento, continuou-se a utilizar o MiniDAQ. Dentre elas está o sistema de teste do detector SciFi.

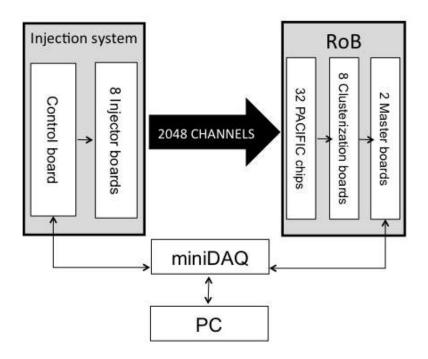

O sistema de teste da eletrônica de *front-end* do SciFi ficou sob responsabilidade do Centro Brasileiro de Pesquisas Físicas (CBPF) quando, em outubro de 2013, o grupo de sabores pesados do Laboratório de Física Experimental (LAFEX) apresentou uma "Expressão de Interesse" em desenvolver e construir um sistema de testes automatizado, para validar o correto funcionamento do detector e seus componentes antes que estes fossem transportados para instalação no LHCb.

O sistema de teste compreende um módulo injetor de sinais, para se ligar à front-end a fim de emular os sinais do detector, e um módulo de aquisição de dados com a finalidade de validar se a front-end efetuou corretamente as etapas de leitura e processamento dos dados. O módulo injetor será produzido pelo CBPF, enquanto o módulo de aquisição será o MiniDAQ.

O objetivo do projeto detalhado nesta dissertação é a validação e preparo do módulo de aquisição (MiniDAQ) para uso no sistema de teste, e a criação de um sistema de controle capaz de configurar individualmente os componentes da *front-end*, utilizando o software de criação de sistemas supervisórios WinCC. Espera-se com os resultados obtidos, que se tenha todas as ferramentas para desenvolver as rotinas automatizadas de teste quando os componentes da *front-end* e o módulo injetor estiverem prontos para produção.

O MiniDAQ, no momento de início do presente trabalho, havia sido produzido recentemente e ainda se encontrava muito instável, com algumas funções em seu software e firmware não funcionando corretamente em ambientes diferentes, e o grupo do CBPF foi o primeiro usuário do módulo. O objetivo de validar o MiniDAQ incluía cooperar, no que fosse possível, para o lançamento de uma versão estável o suficiente para uso no sistema de teste. Isto demandou um extenso trabalho de depuração, relatando os erros e eventualmente possíveis soluções para os desenvolvedores. As correções que este trabalho proporcionou ao MiniDAQ também se estenderiam à PCIe40, por isto o trabalho de depuração também ajudou no desenvolvimento da mesma. O trabalho com o MiniDAQ é detalhado na seção 8.

De posse de um hardware estável e funcional, iniciou-se o desenvolvimento do sistema de controle para o sistema de teste. Enquanto a eletrônica de *front-end* do detector ainda estava em desenvolvimento, foram utilizadas placas alternativas que continham os mesmos componentes a fim de otimizar o tempo de trabalho. Quando o primeiro protótipo da *front-end* foi produzido, em uma semana era possível configurar todos os chips contidos na mesma através do sistema de controle desenvolvido. O desenvolvimento do sistema de controle para o sistema de teste é detalhado na seção 9.

Os capítulos 2 ao 7 tem por finalidade contextualizar o leitor sobre o detector e seus módulos para os quais o sistema de teste está sendo desenvolvido. Os resultados obtidos com a utilização dos elementos descritos neste trabalho são encontrados no capítulo 10 e a conclusão e perspectivas futuras no capítulo 11.

# Capítulo 2

# O Grande Colisor de Hádrons e seus Experimentos

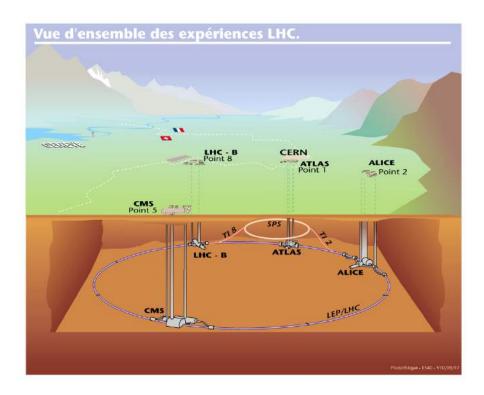

O Grande Colisor de Hadrons (LHC) [1] é o principal acelerador e colisor de partículas do CERN. Localizado na fronteira entre a Suíça e a França, o LHC possui 27 Km de extensão e se encontra em um túnel que varia de 50 a 175 metros de profundidade. O LHC foi projetado para realizar colisões próton-próton e colisões entre íons pesados, a uma energia de até 14 TeV e luminosidade de até  $10^{34}cm^{-2}s^{-1}$ . As colisões ocorrem em 4 pontos específicos e ao redor destes pontos se encontram aparatos de medição que constituem os experimentos do LHC. O LHC possui 7 experimentos: ATLAS [2], CMS [3], LHCb [4], ALICE [5], TOTEM [6], LHCf [7] e MoEDAL.

Objetivo O objetivo do LHC é proporcionar colisões de partículas a energia e luminosidade suficientes para viabilizar a seus experimentos a execução de uma vasta gama de medidas relacionadas a física de partículas elementares a fim de acumular estatística suficiente para responder a questões fundamentais ainda em aberto ou não contempladas pelo modelos atuais que descrevem as interações físicas conhecidas. Entre os tópicos que o LHC visa estudar podemos citar a existência do Bóson de Higgs e suas propriedades, a teoria de supersimetria, a natureza da matéria escura, a violação da simetria entre matéria e anti-matéria e a existência de dimensões extras.

Os Experimentos Os experimentos ATLAS (A Toroidal LHC Apparatus) e CMS (Compact Muon Solenoid) são experimentos de propósito geral, que possibilitaram a descoberta

Figura 2.1: Representação do túnel do LHC e seus 4 principais experimentos.

do Bóson de Higgs no ano de 2012 a partir dos dados acumulados no primeiro run do LHC, e que visam também a busca de fenômenos inconsistentes com o Modelo Padrão.

O experimento ALICE (A Large Ion Collider Experiment) tem por principal objetivo estudar a física de um estado da matéria chamado de plasma de quark-glúons, em que se acredita que o universo se encontrava logo após o Bigbang, e que o LHC tenta reproduzir através da colisão de íons de chumbo. O ALICE também estuda colisões próton-próton para efeitos de comparação com os resultados de íons pesados e outras áreas em que seus resultados são competitivos com os demais experimentos.

O experimento LHCb (*Large Hádron Collider Beauty*) tem por objetivo principal o estudo da violação de simetria Carga-Paridade (CP) nas interações de hádrons B. Tal estudo poderia ajudar a explicar a assimetria de matéria e anti-matéria encontrada no Universo. O LHCb foi também o experimento responsável pela descoberta do Pentaquark em 2015. O experimento LHCb é discutido com mais detalhes na seção 3.

O experimento TOTEM (TOTal Elastic and diffractive cross section Measurement) visa o estudo da estrutura do próton através de medições da seção de choque das interações

proton-proton, sua dispersão elástica e processos difrativos.

O experimento LHCf (*LHC forward*) reliza a medição precisa de partículas neutras originadas das colisões numa direção bem próxima ao feixe, cujo ângulo é próximo de 0°. O estudo visa o melhor entendimento da interação de raios cósmicos com a atmosfera terrestre.

O experimento MoEDAL (the Monopole and Exotics Detector At the LHC) é dedicado à procura de partículas bem específicas, estáveis e exóticas, como monopolos magnéticos, provenientes das colisões próton-próton.

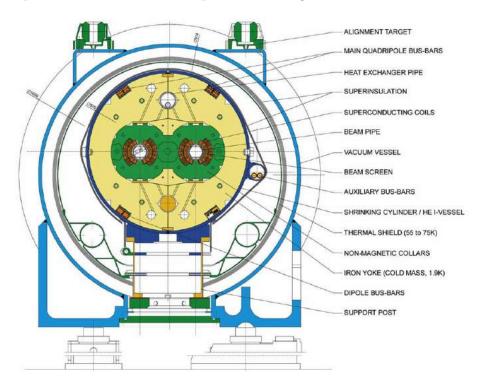

As colisões O LHC possui dois tubos paralelos onde dois feixes de prótons são conduzidos em direções opostas, próximos à velocidade da luz, com energia de até 7TeV cada. Em 4 pontos específicos, a uma frequência de 40MHz (a cada 25ns), os 2 feixes se cruzam ocasionando as colisões com energia total de 14TeV. Cada feixe é composto por 2808 bunches, que trafegam no vácuo existente nos tubos, da ordem de  $10^{-10}$  a  $10^{-11}$  mbar. Na Figura 2.2 é possível ver os dois tubos por onde trafegam os feixes.

Figura 2.2: Corte transversal da vista frontal de um módulo dipolo do LHC.

Ao longo do tubo circular do LHC, os bunches são conduzidos, colimados e ace-

lerados por módulos magnéticos diferentes. O módulo de dipolo magnético é responsável por manter a curvatura do feixe. Este possui um eletro-ímã supercondutor de 15 metros, localizado ao redor de cada tubo, que provê um campo magnético de 8,33T. Para fornecer este campo, o ímã consome uma corrente de 13.000A e é mantido a uma temperatura de 1.9K pelo sistema de criogenia. Mais de 60% da extensão do LHC é composto por estes módulos, totalizando 1232 módulos. A Figura 2.2 mostra o corte transversal de um módulo dipolo. O módulo responsável pelo foco e colimação do feixe é o módulo quadripolo. Já a manutenção e aceleração dos bunches é executada pelas cavidades de radiofrequência, cuja frequência de alternação é sincronizada com os bunches de forma a sempre propiciar aceleração na região onde os bunches devem estar e uma força contrária nas regiões intermediárias, tendendo a conduzir desta forma os prótons para a região central dos bunches.

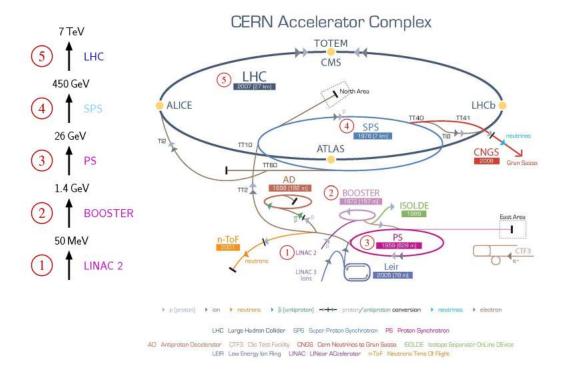

Cadeia de aceleração Os feixes de prótons que circulam no LHC tem sua origem em um cilindro de gás hidrogênio. Os prótons são separados no gás utilizando um equipamento chamado Duoplasmatron, que ioniza o gás através da aplicação de um forte campo elétrico. Os prótons deixam o Duoplasmatron a uma velocidade de 1,4% da velocidade da luz e são enviados a um quadripolo de rádio frequência, que foca o feixe e o acelera até 750keV. Este feixe é inserido em um acelerador linear denominado LINAC2, onde são acelerados até uma energia de 50MeV e então inseridos no "Proton Synchrotron Booster" (PSB). O PSB é um acelerador circular de 4 anéis, o qual acelera o feixe até 1,4GeV. Do PSB, o feixe é inserido no "Proton Synchrotron" (PS) o qual divide o feixe em 81 bunches espaçados e os acelera até 26GeV. Os bunches são então injetados no "Super Proton Synchrotron" (SPS), que os acelera até 450GeV. Os prótons levam, da fonte até a saída do SPS, um tempo inferior a 18s e então são injetados no LHC. Esta injeção ocorre por dois pontos diferentes, cada um destes levando a um dos dois tubos do LHC, inserindo os bunches em sentidos opostos em cada tudo. No LHC, os feixes podem ser acelerados até 7TeV. Conforme veremos no cronograma da Figura 4.1, o LHC até o ano de 2015 operou com uma energia máxima de 6,5TeV por feixe. Planeja-se alcançar colisões de 14TeV até o final do run de 2018.

Após acelerados até a energia desejada, os feixes de sentidos opostos começam então a serem colididos nos quatro pontos de cruzamento já citados. A Figura 2.3 ilustra as etapas de aceleração descritas, mostrando à esquerda a energia alcançada pelo feixe ao fim de cada etapa.

Figura 2.3: Cadeia de aceleração do LHC.

# Capítulo 3

### O Experimento LHCb

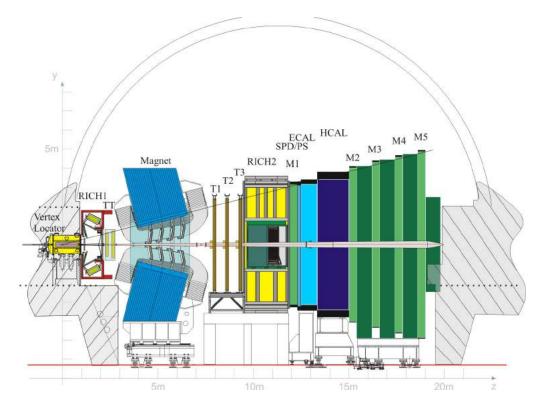

O experimento Large Hadron Collider beauty (LHCb) é um espectrômetro de braço único que cobre a região limitada pelos ângulos de 10mrad até 300mrad no plano horizontal e 10mrad até 250mrad no plano vertical a partir do ponto de colisão. O LHCb se encontra no local denominado como Ponto 8 do LHC, em uma região experimental escavada em torno de um dos 4 pontos de colisão. Ele é composto por um conjunto de detectores e elementos que permitem a identificação de partículas e reconstrução de sua trajetória. Dentre estes, os principais são: o Localizador de Vértice (VeLo), o Sistema de Trajetografia, o Sistema de Múons, o Magneto, os Calorímetros Hadrônicos e Eletromagnéticos, e os detectores Ring-Imaging Cherenkov (RICH).

O objetivo do LHCb é estudar a violação de simetria carga-paridade e processos raros no decaimento de hádrons B produzidos a partir das colisões do LHC.

O LHCb mede 21m de comprimento, por 10m de altura e 13m de largura. Este possui uma geometria frontal, se extendendo na direção do feixe conforme angulação já mencionada, devido à natureza dos hádrons B, que são gerados com momento em direção próxima à da colisão que o gerou. A fim de construir o detector mais eficiente possível com os recursos disponíveis, o experimento foi montado em apenas um dos sentidos da colisão. Desta forma, se perde a metade dos processos, mas sobra mais recursos para criação de um detector que gere resultados mais precisos. Na Figura 3.1 se pode ver a geometria do detector LHCb.

Figura 3.1: Vista lateral do detector do experimento LHCb.

#### 3.1 VeLo

O Localizador de Vértice (VeLo) é o primeiro detector a interagir com o produto das colisões. Este é montado ao redor do ponto de colisão e tem por objetivo fazer a medição das coordenadas de trajetórias na região próxima ao ponto de colisão. As medidas efetuadas pelo VeLo são utilizadas na reconstrução das trajetórias e dos vértices de produção (primários) e de decaimento (secundários) dos mésons B. Os dados do VeLo também são utilizados na filtragem dos eventos, enriquecendo as amostras de mésons B selecionadas.

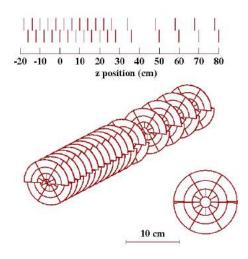

O VeLo é composto por semidiscos instalados ao redor da região de colisão, conforme mostrado na Figura 3.2. Os semidiscos são instalados em um recipiente de vácuo para separar o tubo do LHC da atmosfera da região do experimento. Eles são compostos por detectores de silício que proporcionam uma reconstrução de vértices primários com resolução da ordem de 40  $\mu m$  na direção z e 10  $\mu m$  na direção radial dos semidiscos  $\phi$ . Para vértices secundários a resolução é um pouco pior e pode variar entre 150  $\mu m$  e 300  $\mu m$  dependendo do número de traços utilizados.

Figura 3.2: Geometria do VeLo. Ao todo são 34 semidiscos instalados ao redor da região de colisão.

### 3.2 Magneto

O LHCb possui um magneto cujo principal objetivo é gerar um campo magnético forte o suficiente para curvar as partículas carregadas criadas na colisão de forma que seja significativamente perceptível ao sistema de trajetografia.

Sabendo-se a intensidade do campo magnético e unindo às informações providas pelo sistema de trajetografia (descrito na seção 3.3) é possível medir o momento e a carga relacionada às partículas. Esta medida é crucial para identificação das partículas que atravessam o detector RICH.

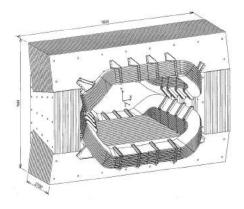

Figura 3.3: Geometria do magneto do LHCb.

O campo magnético é gerado no LHCb por um dipolo localizado próximo ao VeLo e, portanto, próximo à região de colisão. O poder de curvatura do magneto é da ordem de 4 Tm. Isto proporciona uma medição do momento das partículas de até  $\delta p/p = 0.4\%$ , com capacidade de manter o campo magnético uniforme dentro de uma margem de erro de aproximadamente 5% para partículas com ângulo polar entre 250 mrad no plano vertical e 300 mrad no plano horizontal.

### 3.3 Sistema de Trajetografia

O Sistema de Trajetografia é o sistema responsável por fornecer os dados necessários para reconstrução da trajetória de partículas carregadas que atravessam o experimento. Ele fornece uma estimativa de alta precisão do momento das partículas e também uma medida de massa de partículas instáveis. As informações de trajetória do sistema de trajetografia também auxiliam o detector RICH na identificação de partículas.

O Sistema de Trajetografia compreende o detector VeLo, as Estações de Trajetória e também utiliza o Magneto para obtenção da informação de momento e massa. Há 4 estações de trajetória no sistema: TT (*Trigger Tracker*), e as estações de trajetória T (T1, T2 e T3) que estão subdividas em *Inner Tracker* (IT) e *Outer Tracker* (OT). Na Figura 3.1 podemos ver discriminado a posição das estações TT, T1, T2 e T3 no LHCb.

Veremos a seguir que as estações de trajetória seguem um layout que se estende no plano vertical ou desviado de  $\pm 5^{\circ}$  no plano vertical. Isto é feito para se otimizar a resolução espacial no eixo horizontal, em detrimento da resolução no eixo vertical. O eixo horizontal é o eixo de ação do Magneto sob as partículas, e esta estratégia permite medir com mais precisão o desvio causado nas partículas pelo campo magnético e, por consequência, melhorar indiretamente as medidas de momento e massa.

Trigger Tracker A estação TT está localizada antes do magneto e tem como principal objetivo reconstruir partículas de baixo momento que, quando entram na região do magneto, são desviadas para fora da aceptância do LHCb e, portanto, não atingem as estações de trajetória T. Além disso, devido à proximidade com o magneto, a existência de um campo magnético na região da TT permite uma medida de momento menos precisa porém útil para a seleção dessas partículas.

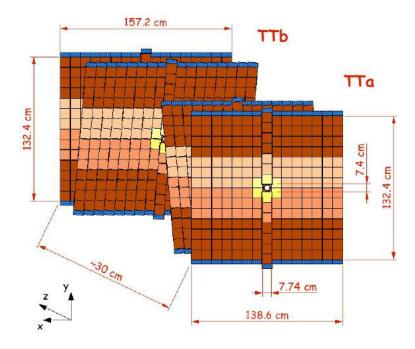

Figura 3.4: Layout dos 4 detectores da estação de trajetória TT.

O TT possui resolução espacial de aproximadamente  $50\mu m$  e é composto por tiras de silício com 11 cm de comprimento, 7.8 cm de largura e 198  $\mu m$  de espessura para fazer a leitura do sinal eletrônico quando uma partícula atravessa o detector. Ao todo são 4 planos, sendo que os dois mais externos têm tiras posicionadas verticalmente e os dois internos possuem tiras posicionadas em ângulos de  $\pm 5^{\circ}$ , dependendo da posição do plano com relação ao tubo por onde passa o feixe. A estrutura desses planos está ilustrada na figura 3.4.

Inner e Outer Tracker O IT compreende a parte interna das estações T1, T2 e T3, que estão localizadas entre o magneto e os calorímetros. O OT compreende a parte externa das estações T1, T2 e T3. Os principais objetivos dos IT e OT são reconstruir a trajetória das partículas entre o VeLo e os calorímetros e medir o momento com o auxílio do magneto, medir com precisão o local onde as partículas atingem o RICH e conectar as medidas feitas pelo VeLo com as obtidas nos calorímetros. O IT e OT estão representados na figura 3.5.

O IT têm o mesmo formato , resolução e composição das TT e juntas são chamadas de *Silicon Tracker* no LHCb, devido à utilização de silício em seus detectores. O OT possuem resolução espacial de aproximadamente  $200\mu m$  no eixo horizontal e é composto

Figura 3.5: Posicionamento das estações de trajetória. Em roxo na parte inferior esquerda se encontra o TT. Na parte à direita, se encontra as 3 estações T1, T2 e T3. Em roxo, ao centro das estações T, se encontra o Inner Tracker. O restante das estações T, em azul claro, são as camadas do Outer Tracker.

por câmaras de arrasto em formato cilíndrico com 5 mm de diâmetro e 0.075 mm de espessura. A cobertura total do OT chega a uma região de 600  $cm \times 490$  cm enquanto que as IT cobrem a parte interna (região ao redor do feixe), uma região de aproximadamente 120  $cm \times 40$  cm.

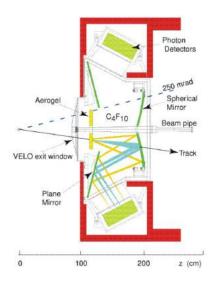

#### **3.4** RICH

O Ring Imaging Cherenkov (RICH) [8] é o detector responsável pela identificação de partículas carregadas com momento na faixa de 1GeV até 150GeV, tendo o auxílio do sistema de trajetografia. O seu funcionamento está fundamentado na radiação Cherenkov, que é a radiação emitida por partículas que possuem uma velocidade maior que a velocidade da luz no meio em que se propagam. Essa radiação emitida é então capturada após ser seguidamente refletida por espelhos dentro do RICH e tem seus ângulos de emissão e reflexão medidos. Com essas informações é possível medir a velocidade com que a partícula entrou no detector. Sabendo-se o momento então é possível determinar a massa e, a partir

desta, a identidade da partícula.

O LHCb possui 2 detectores do tipo RICH: o RICH1 está localizado logo após o VeLo e opera na faixa de 1GeV até 65GeV enquanto o RICH2 fica logo após as estações de trajetória e opera na faixa de 15GeV até 150GeV.

Figura 3.6: Vista lateral do detector RICH1.

#### 3.5 Calorímetro

Os calorímetros são detectores que tem por objetivo medir a energia depositada pelas partículas que são desaceleradas ao atingirem o calorímetro. O LHCb possui dois tipos de calorímetros [9]: o Hadrônico (HCAL) e o Eletromagnético (ECAL). O HCAL tem por objetivo a identificação de partículas cuja interação principal é dada pela força forta, enquanto o ECAL visa a identificação de partículas que interagem por força eletromagnética.

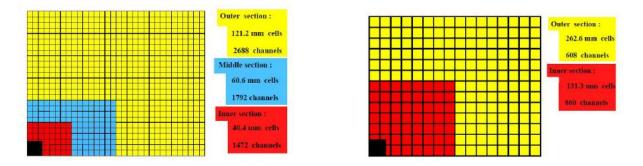

O sistema de calorímetros ainda compreende o *Scintillating Pad Detector* (SPD) e *Pre-Shower Detector* (PS). O SPD é responsável pela identificação de partículas neutras ou carregadas enquanto que o PS difere entre estas partículas elétrons (carregada) e fótons (neutra). Na Figura 3.7 podemos ver a distribuição das células nos calorímetros do LHCb.

A estrutura do calorímetro varia de acordo com seu componente. O SPD, PS e ECAL são compostos por células organizadas em uma mesma estrutura, ilustrada na

Figura 3.7: Ilustração da granularidade nos SPD, PS e ECAL (esquerda) e no HCAL (direita).

figura 3.7. O tamanho de cada célula é de  $4\times 4$  cm na parte interna do detector,  $6\times 6$  cm na parte intermediária e  $12\times 12$  cm na parte externa. As células do SPD e do PS são placas cintiladoras de 15 mm de espessura conectadas à fotomultiplicadora por fibra ótica. Já o ECAL alterna placas cintiladoras de 4 mm de espessura e pratos de chumbo de 2 mm de espessura. O HCAL alterna placas cintiladoras de 4 mm de espessura com pratos de ferro de 16 mm de espessura.

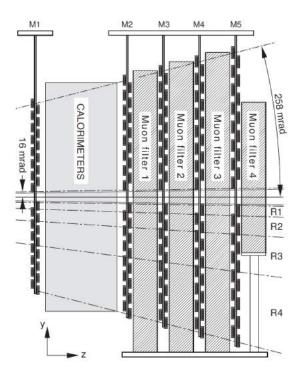

### 3.6 Sistema de Múons

O sistema de múons [10] é um conjunto de detectores formando 5 estações de múons (M1 a M5), que tem por objetivo fazer a medição da trajetória dos múons que atravessam o experimento. Este fica localizado ao final do experimento devido ao fato dos múons serem as únicas partículas que não são contidas pelo calorímetro. O sistema de múons cobre toda a aceptância do experimento e uma área de aproximadamente  $435\ m^2$ . A estação M1 está localizada à frente do PS enquanto que as outras 4 estações estão localizadas logo após o HCAL, separadas por filtros de ferro com as mesmas dimensões. Ao todo existem 1380 câmaras, de 20 tamanhos diferentes, instaladas de acordo com a ocupação de partículas nas diferentes regiões da estação.

Cada câmara de múons é composta por células preenchidas com uma combinação de 3 gases: dióxido de carbono, argônio e tetrafluorometano. Ao atravessar uma célula, o múon ioniza essa combinação de gases e um eletrodo localizado no centro da célula captura os elétrons resultantes da ionização, gerando uma corrente que é medida pela eletrônica de front-end do detector.

A Figura 3.8 mostra a posição das 5 estações de múons no experimento.

Figura 3.8: Vista lateral do sistema de múons, indicando a posição das estações M1 a M5.

### 3.7 Trigger

O sistema de *Trigger* do LHCb é o sistema responsavel por filtrar quais dentre os eventos terão ou não seus dados armazenados no *cluster* de armazenamento do LHCb.

Os detectores do LHCb capturam os eventos na mesma taxa em que ocorrem as colisões: 40MHz. O volume de dados gerados a cada evento é muito grande e a eletrônica utilizada para envio e aquisição de dados no experimento não possuem largura de banda suficiente para recuperação dos dados de todas as colisões. Por esta razão, os eventos são filtrados a fim de selecionar apenas os mais relevantes para o propósito do experimento. O objetivo final do Sistema de Trigger é reduzir a taxa de armazenamento de eventos de 40MHz para a ordem de kHz. O sistema é dividido em duas partes: o Level-0 Trigger (LO) e o High-Level Trigger (HLT).

LO O Trigger de nível 0 é um trigger implementado a nível de hardware. Este recebe dados diretamente dos detectores para efetuar a decisão de manter ou não o evento. O objetivo do LO é reduzir a taxa de eventos a 1MHz. O LO é implementado em módulos eletrônicos na região do experimento.

O Trigger L0 recebe informações do VeLo, dos calorímetros, do sistema de múons e do sistema de *Pile-up*, que é um sistema responsável por identificar empilhamento de sinais nos mesmos canais dos detectores. Os critérios para decisão do sistema de trigger são baseados nos seguintes parâmetros:

- Energia total depositada nos calorímetros hadrônicos e eletromagnéticos.

- Momento transverso das trajetórias reconstruídas nas estações de múons.

- Identificação da partícula pela leitura dos calorímetros.

- Multiplicidade do número de trajetórias que atingem os calorímetros.

- Número de vértices primários e de trajetórias provenientes de um segundo vértice.

O valores de corte para cada um destes parâmetros são ajustados de forma a garantir a redução de eventos para o valor máximo desejado de 1MHz.

HLT O Trigger de Nível Superior é um trigger implementado a nível de software. O mesmo se trata de algoritmos que são executados nos computadores da sala de contagem, que recebem os dados do experimento e efetuam a reconstrução a fim de identificar candidatos a méson B de interesse. O filtra aplicado pelo HLT reduz o número de eventos enviados para armazenagem a uma taxa de poucos kHz.

#### 3.8 Sistema Online

O Sistema Online do LHCb compreende todos os aspectos de computação *online* e os sistemas de controle do experimento LHCb. Ele provê a infraestrutura para a tomada de dados para os Triggers de alto nivel (HLT), assim como para controle, configuração e monitoramento de todo o experimento.

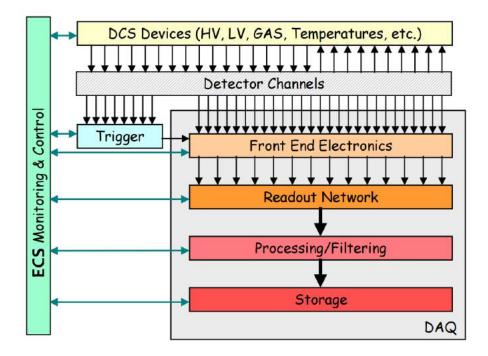

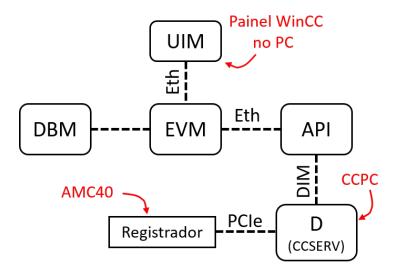

O Sistema Online compreende três componentes: DAQ (Data Acquisition System), o TFC (Trigger and Fast Control) e ECS (Experiment Control System).

**DAQ** O Sistema de Aquisição de Dados tem por objetivo transportar os dados proveniente dos detectores até o local de armazenagem permanente. Como visto na seção 3.7, apenas uma pequena parte dos dados é armazenada. A aquisição é engatilhada pelo Trigger de Nível 0 (L0) e o DAQ é responsável por garantir o envio de todos os dados referentes ao evento indicado pelo L0.

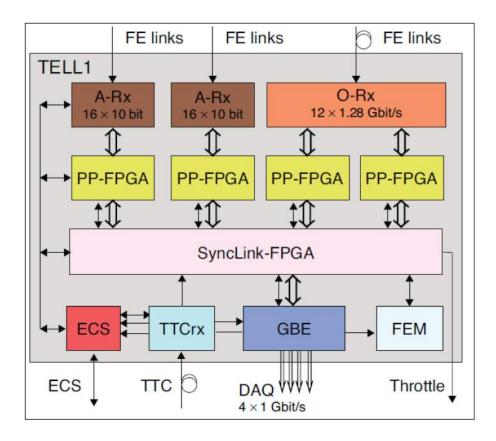

A leitura dos detectores é efetuada pela eletrônica de front-end e os dados são enviados a módulos eletrônicos de leitura chamados TELL1. Os dados recebidos pelo TELL1 são processados em quatro FPGAs. Nos FPGAs os dados são processados de acordo com a necessidade do detector de origem, podendo ser aplicada compressão de dados, supressão de zeros entre outros algoritmos. Após o processamento, os dados são coletados por um quinto FPGA (SyncLink) e formatados em um pacote raw IP, que é enviado ao sistema de aquisição de dados através de um módulo Gigabit-Ethernet de quatro canais. A interface com o ECS é feita através de um CCPC (Credit Card PC) montado como mezzanino na TELL1. Os sinais de sincronismo e clock são transmitidos através da interface de Trigger, Timing and Control (TTC). O fluxo de dados para o TFC é realizado através do sinal de trottle e é conduzido pelo FPGA SyncLink. O diagrama de blocos simplificado é apresentado na Figura 3.9.

**TFC** O Sistema de *Trigger and Fast Control* (TFC) é o sistema responsável por distribuir o clock de sincronismo do feixe do LHC, as decisões do *trigger* L0, sinais síncronos de reset e comandos de *fast control*. O TFC trata todos os estágios da leitura dos dados entre a eletrônica de *front-end* e os computadores de aquisição na sala de contagem. Ele não apenas distribui os sinais mas também garante que sinais como de trigger, de reset e de clock cheguem aos módulos de destino de forma síncrona.

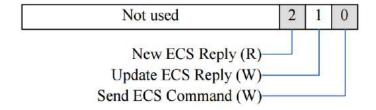

ECS O Sistema de Controle de Experimento (ECS) é o sistema responsável pela configuração, controle e monitoramento operacional de todos os componentes do sistema online e dos detectores. Ele provê formas de enviar comandos aos diferentes equipamentos do sistema e de efetuar operações de escrita e leitura em registradores.

O ECS abrange alguns protocolos, dentre eles o Serial Protocol for ECS (SPECS), que é um protocolo próprio desenvolvido no CERN, Controller Area Network (CAN) e Ethernet, mas não se limita a estes padrões e para alguns dispositivos foi criado uma solução customizada para interface com o sistema ECS. O ECS é um sistema complexo,

Figura 3.9: Diagrama de blocos simplificado do módulo de aquisição TELL1.

que compreende os módulos que fazem a comunicação com os equipamentos finais, os drivers para interface com estes módulos e um sistema de controle baseado no software WinCC da Siemens, que provê meios de gerenciar todos os módulos do sistema e fornece a interface com o usuário. Mais sobre o funcionamento de um sistema de controle WinCC é explicado na seção 9.

Dentre os itens controlados pelo ECS, podemos citar:

- Operações de detector

- Sistema de distribuição de gás

- Módulos de alta tensão

- Módulos de alimentação

- Controle de temperatura

- Sistemas de *Trigger* e DAQ

- Eletrônicas de front-end

- Reconstrução de eventos

- Parâmetros de filtragem do HLT

- Infraestrutura do experimento

- Sistema de ventilação e refrigeração

- Distribuição elétrica

- Controle do Magneto, Sistemas do Acelerador, Sistemas de Segurança e etc.

Na Figura 3.10 temos uma ilustração simplificada do sistema de controle e sua cadeia de contole.

Figura 3.10: Escopo de controle do sistema ECS, mostrando as diferentes operações controladas em paralelo pelo ECS.

### Capítulo 4

# Upgrade do LHCb

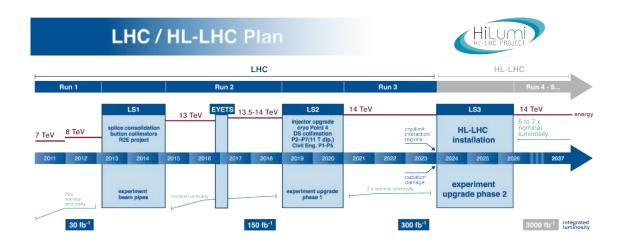

Definição O LHC passará por uma atualização durante o período LS2 e LS3 que visam o aumento de sua luminosidade de 5 a 7 vezes a luminosidade nominal para a qual foi projetado. O projeto do novo LHC foi chamado de "High Luminosity LHC" (HL-LHC) [11]. Na Figura 4.1 se pode ver o cronograma de operação do LHC / HL-LHC para os próximos anos. De forma complementar, o experimento LHCb também sofrerá atualizações a fim de se adequar aos novos regimes de maior luminosidade que serão oferecidos pelo acelerador LHC. O LHCb terá seu upgrade realizado durante a próxima interrupção longa (LS2) do LHC, que está previsto para os anos de 2019 e 2020, tendo seu retorno em 2021.

Figura 4.1: Cronograma de operação do LHC para os anos seguintes.

Resultado esperado. Com o upgrade do LHCb, espera-se elevar o seu rendimento físico em decaimentos com muon por um fator de 10, o rendimento dos canais hadrônicos por um fator de 20 e coletar dados a uma luminosidade aproximada de  $1-2\times 10^{33}cm^{-2}s^{-1}$ . Isto corresponde a dez vezes a luminosidade do projeto atual e permitirá ao LHCb elevar o seu volume de dados coletados anualmente do atual  $1fb^{-1}$  de luminosidade integrada para 5 a  $10fb^{-1}$ . Uma Carta de Interesse [12], um TDR de Framework [13] e um TDR de Trigger e Online [14] documentam os planos para uma atualização dos componentes do experimento.

Atualizações O upgrade do LHCb será baseado na extinção do trigger de nível 0 e aquisição de dados a uma taxa de 40MHz. O aumento na luminosidade do LHCb trará como consequência a elevação significativa do nível de radiação incidente, do volume de dados gerados e da ocupação nos canais dos detectores, entre outras. Os novos níveis de radiação exigem a validação de todos os componentes do sistema e o uso de eletrônica apropriada. O volume de dados exige substituição de toda eletrônica de aquisição do experimento e também da eletrônica de front-end (FEE) dos detectores. Por ter a FEE embutida no módulo de detecção, os detectores VELO, IT, TT e RICH também terão de ser substituídos. O novo nível de ocupação no detector Outer Tracker exige uma reformulação completa de sua arquitetura.

#### 4.1 GBT

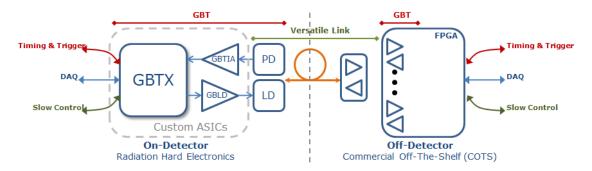

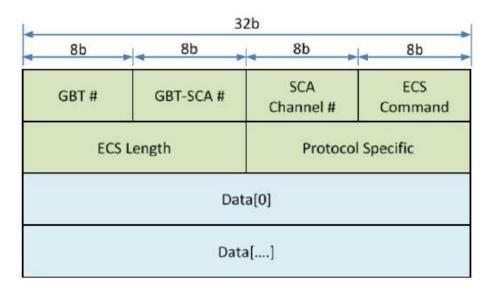

O GBT (GigaBit Transceiver) se refere a um projeto com o objetivo de desenvolver um conjunto de circuitos integrados (chipset) resistentes a radiação para permitir a implementação de um link óptico bidirecional de 4.8Gbps a ser utilizado no upgrade do LHC. O link implementado pelo GBT visa a transmissão de dados entre a eletrônica de front-end e back-end, atendendo simultaneamente aplicações como aquisição de dados, trigger, temporização e controle. O GBT possui um protocolo próprio de comunicação. No projeto GBT há um ramo chamado projeto GBT-FPGA que visa o desenvolvimento de um código HDL que permita a interface direta entre FPGAs e links baseados no GBT.

O chipset GBT compreed os seguintes circuitos integrados:

• GBTx é o chip que serializa e desserializa os dados do link, e implementa a camada

de protocolo do link, sendo responsável pela codificação e decodificação dos dados.

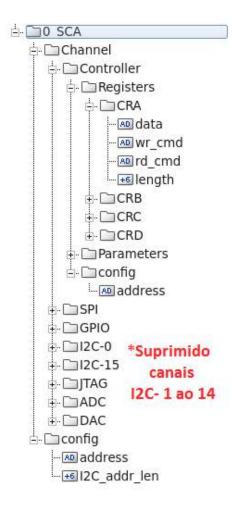

- GBT-SCA (*GBT-Slow Control Adapter*) é um chip responsável por fornecer interfaces de controle ao sistema. O GBT-SCA traduz comandos recebidos pelo link GBT em comandos em protocolos comuns utilizados para controle como I2C, SPI e JTAG. Adicionalmente o mesmo possui conversores analógico-digitais e digital-analógicos que podem ser utilizados para diferentes propósitos.

- GBTIA é um amplificador de transimpedância cujo objetivo é amplificar a corrente proveniente do diodo PIN. Ele opera a uma taxa de até 5Gbps e foi desenvolvido para lidar com a degradação de sensibilidade do diodo PIN devido a incidência de radiação.

- GBLD é o circuito integrado responsável por alimentar o transmissor com os dados, modulando a corrente fornecida ao laser para alcançar a melhor conversão eletroóptica.

No upgrade do experimento LHCb, os chips GBT são utilizados na eletrônica de front-end, a fim de suprir a necessidade de um link óptico de alta velocidade e resistente a radiação. Já na eletrônica de aquisição, que fica em área sem incidência da radiação do LHC, não é necessário a utilização dos chips. Neste caso utiliza-se um módulo óptico comercial e a camada de protocolo do GBT é implementada em FPGA. O objetivo disto é reduzir o custo com a produção de circuitos integrados de aplicação específica. Na Figura 4.2 podemos ver o diagrama da implementação de um link GBT.

Figura 4.2: Diagrama apresentando aplicação dos chips do projeto GBT.

O GBT foi desenvolvido de forma a minimizar a perda de dados por "Single Event Upsets" (SEU), que é alteração do estado lógico de uma célula de memória (um bit de um

registrador, por exemplo) pela passagem de uma partícula ionizante. O GBT é produzido utilizando tecnologia CMOS de 130nm, que é menos susceptível a SEUs, e implementa uma arquitetura de tripla redundância. Esta consiste em criar 2 registradores adicionais para cada registrador original, que recebem sempre o mesmo valor, mas sempre que a alteração de algum deles, estes serão reescritos com o valor predominante. Desta forma para haver perda de dado por SEU, seria necessário que ocorresse um SEU no mesmo bit de 2 registradores diferentes.

O chip GBTx recupera sinal de clock do próprio link GBT. Isto significa que não é necessário um sinal de clock compartilhado. Os mesmos precisam apenas estar operando na mesma frequência. Uma PLL interna do GBTx receptor se calibra em função das bordas do sinal de dados recebido e a partir disto gera um clock para o desserializador.

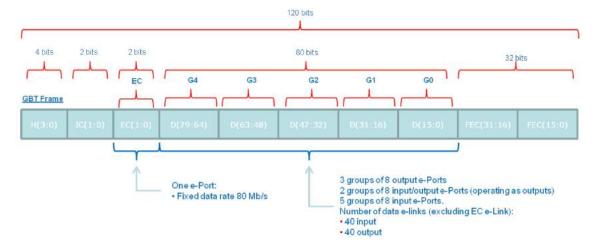

O protocolo GBT é composto por palavras de 120 bits e fornece 3 configurações diferentes: o modo GBT, o modo WideBus, e o modo 8B/10B. No modo 8B/10B, os 120 bits da palavra GBT são simplesmente divididos em 12 palavras na decodificação 8B/10B. No modo GBT, 4 bits são dedicados a um cabeçalho que indica se a palavra é referente a dados válidos ou não, 4 bits são dedicados a controle, 80 bits são dedicados a dados e 32 bits são reservados para um algoritmo de correção de erro. A Figura 4.3 mostra o formato da palavra no modo GBT. O Modo WideBus tem os 4 bits de cabeçalho e controle como o modo GBT, no entanto, ele utiliza todos os 112 bits restantes para dados, abrindo mão do sistema de correção de erro.

Figura 4.3: Estrutura da palavra de 120 bits do protocolo GBT.

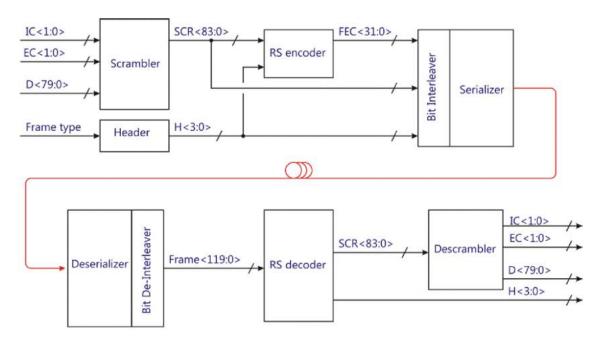

O codificador do GBT é composto por 3 etapas: scrambler, RS Encoder e Interleaver. Podemos ver o diagrama de blocos do codificador e decodificador na Figura 4.4. O

RS Encoder (Codificador Reed-Solomon) só é utilizado no modo GBT e ele é o responsável pelo sistema de correção de erro. O scrambler é um algoritmo que troca os valores dos bits baseado nas palavras anteriores e numa palavra semente, cujo objetivo é impedir que, numa sequência de dados composta predominantemente por '0' ou '1', o valor DC médio do meio de transmissão não fique próximo a Gnd ou Vcc. Isto é um procedimento usado em padrões de comunicação para impedir a carga ou descarga completa de um capacitor de acoplamento que esteja na linha de dados, podendo causar um sinal alto ou baixo contínuo no receptor. O Interleaver é um algoritmo que troca a posição de bits específicos, com o objetivo de facilitar a reconstrução da palavra quando ocorre a perda de bits em sequência.

Figura 4.4: Diagrama de blocos do codificador e decodificar do GBT-FPGA.

### 4.2 Trigger e DAQ

Uma das maiores limitações do experimento atual é a necessidade de reduzir o número de eventos a serem lidos para uma taxa de 1.1MHz. Esta redução é alcançada através dos parâmetros de filtragem do trigger L0. Este é atualmente o maior gargalo na geração de resultados do experimento, e o principal fator que impede que o LHCb faça proveito do regime de maior luminosidade que o upgrade do LHC irá oferecer. Por esta razão, foi decidido que o trigger L0 seria eliminado completamente, e a leitura do

experimento seria realizada a uma taxa de 40MHz, a mesma das colisões, sem nenhuma filtragem a nível de hardware. A leitura dos eventos será transmitida diretamente para a eletrônica de *back-end* e a filtragem dos eventos será dada inteiramente pelo HTL, a nível de software. Um trigger implementado completamente por software adiciona um enorme grau de flexibilidade na escolha de eventos, permitindo que o experimento altere completamente os parâmetros base para a filtragem de eventos, antes limitado pelas conexões físicas do *trigger* L0.

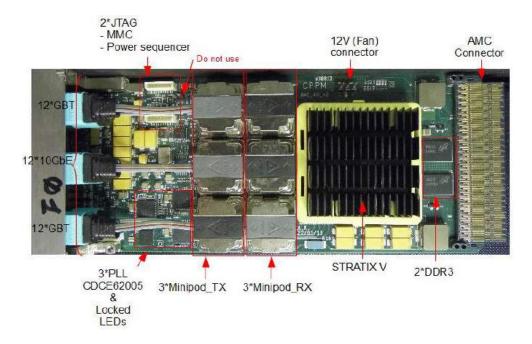

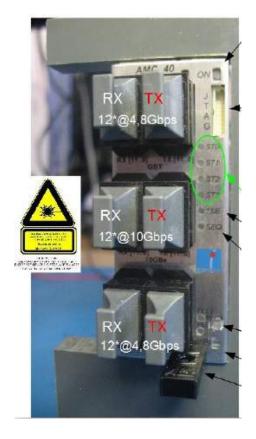

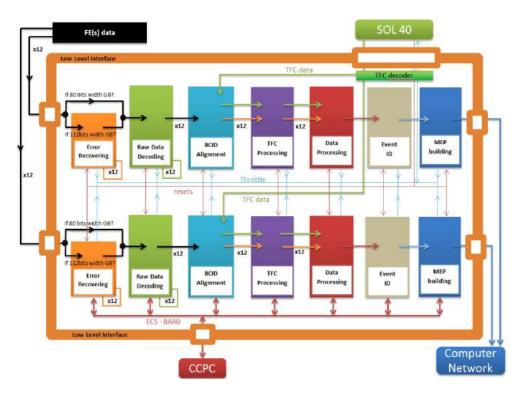

A extinção do trigger L0 com leitura a 40MHz acarreta a substituição de toda eletrônica de aquisição de dados do experimento. Inicialmente, o formato pensado para o sistema de aquisição foi similar ao utilizado atualmente pelo experimento, mas tendo por principal diferença a largura de banda que suportaria um volume de dados bem maior. Este seria composto por um módulo mãe do padrão ATCA (Advanced Telecommunications Computing Architecture) que seria equipada com quatro módulos mezzaninos do padrão AMC (Advanced Mezzanine Card) e que recebeu o nome de AMC40. A AMC40 seria a interface entre a eletrônica de front-end e a rede de computação. Esta ficaria na sala de contagem e transmitiria os dados para a rede através de links ethernet. Cada AMC40 é capaz de processar dados a uma taxa de 108Gbits/s. Ela poderia ser utilizada tanto como módulo de aquisição de dados como também módulo de controle (TFC e ECS), dependendo da forma como é configurado seu FPGA.

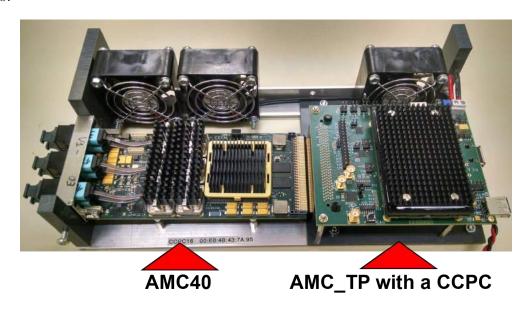

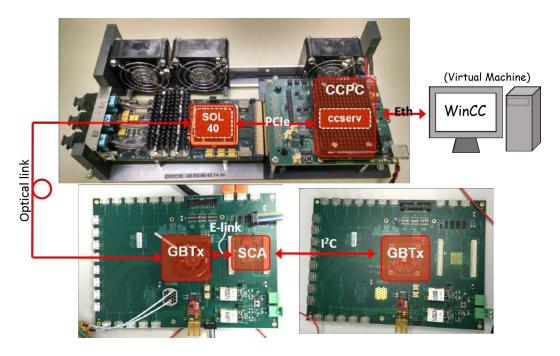

A AMC40 teve algumas unidades fabricadas que foram entregues montadas em uma plataforma de teste chamada MiniDAQ, que era composta por um módulo contendo um CCPC (*Credit Card PC*) e um conector AMC que permitia a utilização da AMC40. O MiniDAQ e a AMC40 foi o sistema escolhido para ser utilizado no Sistema de Teste da Eletrônica do SciFi, sendo a ferramenta principal na realização do trabalho desta dissertação. O MiniDAQ e a AMC40 são explicados com mais detalhes no Capítulo 8

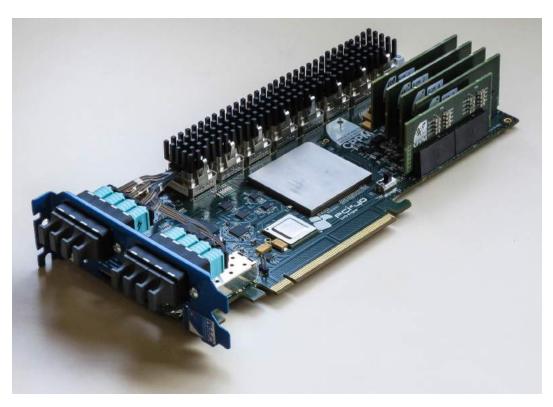

Em um momento posterior, um novo formato para o sistema de aquisição foi pensado. Um módulo de aquisição chamado PCIe40. Esta será a solução utilizada no experimento após o upgrade. Ela é semelhante à AMC40, mas possui um conector PCI express ao invés do conector AMC e um FPGA de maior capacidade. Esta foi desenvolvida com o intuito de embarcar a interface com a eletrônica de *front-end* nos próprios servidores que recebem os dados, por esta razão o conector PCI express.

A PCIe40 é composta por um FPGA Arria 10, 24 links ópticos de entrada para aquisição de dados e 12 links bidirecionais para controle e a interface PCIe a qual permite

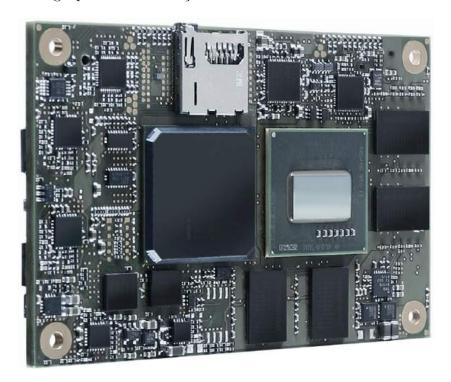

conectá-la ao servidor para que seja feito a coleta dos dados. Há também uma versão de 48 links bidirecionais, usado somente para controle. Cada PCIe40 pode processar uma taxa máxima de dados de 100Gbits/s. Devido ao fato de que a PCIe40 será instalada em região sem incidência de radiação, não há necessidade de se utilizar os chips e componentes ópticos do projeto GBT. A PCIe40 utiliza módulos transceptores ópticos comerciais chamados MiniPODs e para decodificação, utiliza instâncias do firmware GBT-FPGA implementadas no FPGA Arria 10. A imagem de um protótipo da PCIe40 pode ser visto na Figura 4.5.

Figura 4.5: Protótipo da placa de aquisição PCIe40 a ser utilizada no experimento LHCb.

#### 4.3 Upgrade dos Detectores Inner e Outer Tracker

As estações de trajetória T1, T2 e T3, formadas pelos detectores *Inner* e *Outer Tracker*, foram projetadas para prover sua melhor performance em colisões próton-próton com energia de centro de massa de 14TeV ocorrendo a cada 25ns (40MHz), e com luminosidade instantânea de no intervalo de aproximadamente  $2-5\times 10^{32}cm^{-2}s^{-1}$ . O LHCb após o upgrade irá operar com luminosidade superior, na faixa de  $1-2\times 10^{33}cm^{-2}s^{-1}$ . A

geometria do sistema de trajetografia atual foi escolhida de forma que a máxima ocupação nas regiões mais quentes do  $Outer\ Tracker$  fosse limitada a 10% quando sob luminosidade de  $2\times 10^{32}cm^{-2}s^{-1}$ . Esta limitação é estabelecidade pela eficiência do algoritmo de reconstrução de trajetórias mediante elevada luminosidade. Melhorias foram feitas neste algoritmo que permitiram o  $Outer\ Tracker$  a operar com até 25% de ocupação sem perdas na eficiência da reconstrução de trajetórias, mas ainda assim, esta ocupação equivale a uma luminosidade de  $5\times 10^{32}cm^{-2}s^{-1}$ , que ainda é de 2 a 4 vezes menor que a luminosidade esperada no upgrade. Por esta razão surgiu a necessidade de troca dos módulos do  $Outer\ Tracker$  nas regiões de maior luminosidade. Toda a eletrônica de front-end também precisaria ser trocada para se adequar aos novos requisitos de leitura a  $40 \rm MHz$ .

Discutiu-se diversas possibilidades de acordo com os requerimentos do detector para o upgrade até que foi decidido a troca completa dos *Inner e Outer Tracker* por um detector formado por fibras cintilantes e com leitura realizada a partir de fotomultiplicadoras de silício (SiPM). Os principais requisitos deste novo detector estão listados a seguir:

- A eficiência de detecção deve ser superior a 99%.

- A resolução espacial no plano de atuação do magneto deve ser menor ou igual a  $100\mu m$ .

- A eletrônica de leitura do detector deve operar a 40MHz e fornecer uma taxa de amostragem equivalente.

- O detector deve ser capaz de operar com a performance requisitada por uma luminosidade integrada de ao menos 50fb<sup>-1</sup>.

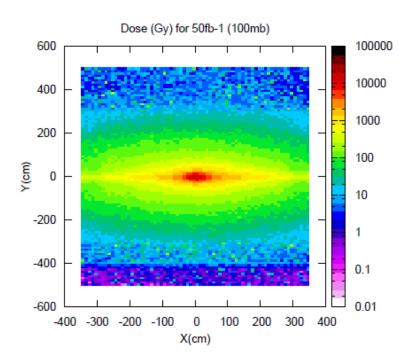

O detector também deve ser limitado em dimensões a fim de caber no espaço ocupado pelo detector atual. O detector deve tolerar os níveis de radiação durante o tempo previsto de operação. O nível de radiação esperado no detector após luminosidade integrada de 50fb<sup>-1</sup> na região de pico, conforme estudo e realizado em [15], é de aproximadamente 35kGy e 25kGy nas estações T1 e T3 respectivamente. Na Figura 4.6 podemos ver o gráfico desta radiação esperada no plano x-y, distando 783cm do ponto de colisão. Esta posição é atualmente a face do Outer Tracker da estação de trajetória T1.

O detector de fibras cintilantes já se encontra em fase de desenvolvimento e será abordado com detalhes no Capítulo 5.

Figura 4.6: Dose esperada no plano x-y a uma distância z=783cm após uma luminosidade integrada de  $50 {\rm fb^{-1}}$ .

# Capítulo 5

## O Detector de Fibras Cintilantes

O Detector de Fibras Cintilantes (SciFi) é um detector de trajetória de partículas carregadas, com eficiência superior a 99% e resolução espacial ao longo do eixo de influência do magneto inferior a  $60\mu m$ . O SciFi é o detector responsável por determinar as coordenadas em que as partículas carregadas cruzaram as estações de trajetória T1, T2 e T3. O objetivo do SciFi é fornecer as informações necessárias para reconstrução das trajetórias, determinação da massa e momento de partículas carregadas que atravessam o detector, e servir informações de posição das partículas necessárias ao sistema de identificação de partículas. Os parâmetros de massa e momento são indiretamente medidos graças à força aplicada pelo campo magnético do magneto, que modifica a trajetória das partículas.

O detector SciFi consistirá em três estações de trajetória, entre o magneto e o detector RICH2. Cada estação do SciFi será composta por 4 camadas de detecção. As 3 estações são centradas no mesmo ponto no eixo z, que é o centro do tubo do LHC. As camadas de detecção de cada estação se encontram, em sequência, nos ângulos 0°, +5°, -5° e 0° em relação ao eixo vertical, correspondendo aos planos X, U, V e X respectivamente. Há um espaço de 20cm entre cada camada de cada estação, e há um orifício circular no centro do detector pelo qual passa o tubo do feixe do LHC.

A pequena diferença de ângulo entre os planos de detecção é feita para maximizar a resolução na direção em que o magneto desvia as partículas, uma vez que a medida de massa e momento depende apenas do valor nesta direção. Por consequência, há um detrimento da resolução espacial no eixo y.

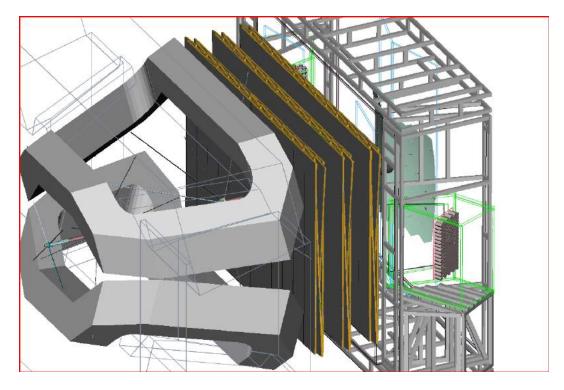

A Figura 5.1 apresenta um modelo 3D do detector, entre o magneto e o RICH2.

Figura 5.1: Modelo 3D das 3 estações que compõem o detector de fibras cintilantes, mostrado entre o magneto (à esquerda) e o detector RICH2 (estrutura à direita).

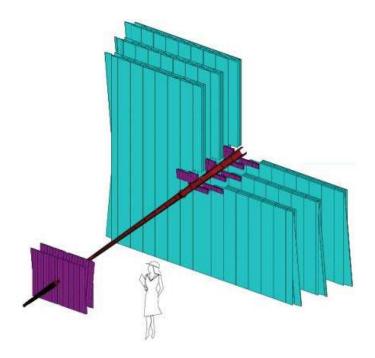

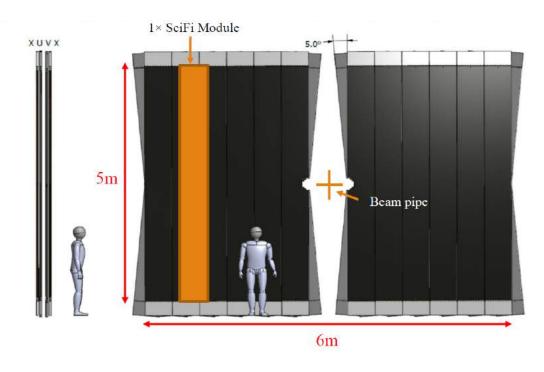

Cada camada de detecção é subdividida em 12 módulos de fibras cintilantes. Cada módulo possui 5m de altura por 0,52m de largura. O detector completo cobre a área de 5m de altura por 6m de largura, no plano X-Y. Ao total, o detector SciFi compreende 144 módulos.

A Figura 5.2 mostra como é o arranjo dos módulos e um comparativo de tamanho com uma pessoa de estatura média.

### 5.1 Composição de um Módulo do Detector

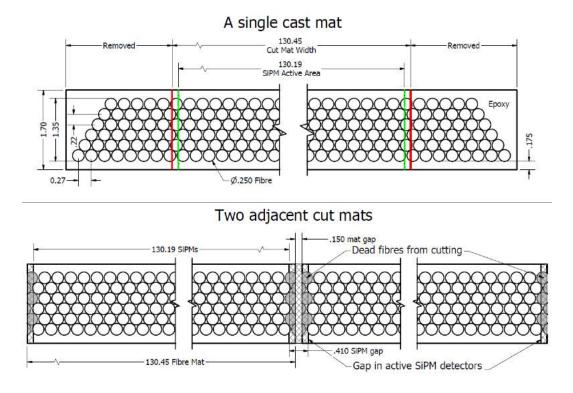

Cada módulo do detector é subdividido em oito *mats* de fibras cintilantes com 2,5m de comprimento. Quatro *mats* são postos lado a lado na parte superior e quatro na parte inferior. Os módulos que ficam no centro serão ligeiramente modificados para acomodar o tubo do feixe do LHC que cruza o centro do detector. Os *mats* são estruturas de 13cm de largura onde são coladas as fibras. As fibras são coladas de forma empilhada, encaixadas entre si, formando 6 camadas de fibras conforme visto na Figura 5.3.

Figura 5.2: Modelo 3D do arranjo dos módulos do detector SciFi.

Figura 5.3: Ilustração do agrupamento da fibras em um  $\mathit{mat}$ .

Nas extremidades externas de cada módulo de fibra há um módulo de leitura chamado Read-Out Box (ROB), que abriga toda a eletrônica que efetua a leitura do detector. Nas extremidades internas, que ficam voltadas para o centro do detector, há espelhos para que a luz conduzida nesta direção seja refletida para a extremidade oposto onde há o módulo de leitura.

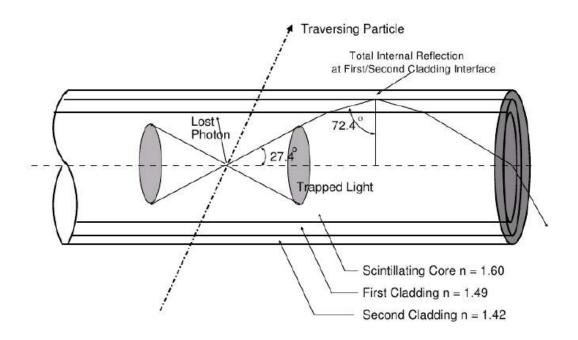

#### 5.2 As Fibras Cintilantes

As fibras cintilantes são o elemento ativo de detecção do projeto SciFi. Estas são fibras de  $250\mu m$  de diâmetro com um núcleo de poliestireno revestido com duas camadas cujos índices de refração são decrescentes de dentro para fora. A camada de revestimento interior é formada por polimetil-metacrilato (PMMA) e a camada exterior é feita de um polímero fluoretado. O projeto das camadas de revestimento das fibras são feitos de modo a otimizar a reflexão interna de luz, fazendo com que esta seja guiada pela fibra para as extremidades, onde são lidas por um sensor óptico. O núcleo das fibras é feito de material cintilante. Algumas partículas, ao cruzarem este material, depositam energia no mesmo, excitando os átomos ali contidos e causando uma reação que emite luz, a qual é chamada de cintilação.

A Figura 5.4 mostra uma ilustração da fibra com suas camadas e o índice de refração de cada uma destas.

### 5.3 Módulos de Leitura

No final de cada módulo de fibra como os vistos na Figura 5.2, é anexado um módulo de leitura que recebe o nome de "Read-out Box" (ROB). Os ROBs são estruturas onde estão contidos os elementos de leitura do detector.

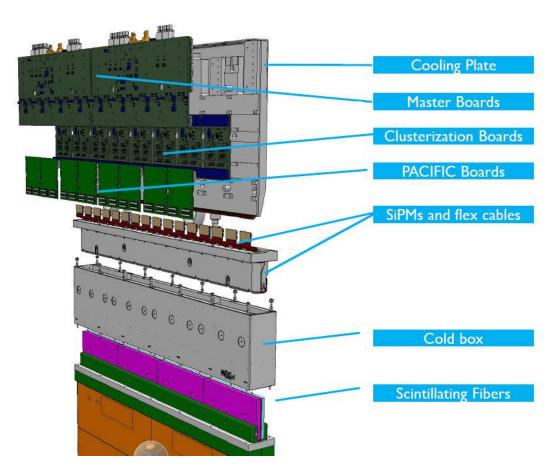

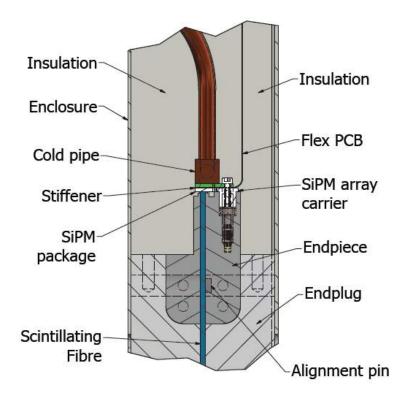

Um ROB é composto por uma *Cold Box*, que abriga 16 Fotomultiplicadoras de Silício (SiPM), e dois módulos da eletrônica de *front-end* (detalhada no Capítulo 6). A Figura 5.5 apresenta a visão explodida de um ROB, indicando seus diferentes componentes.

Uma das principais funções do ROB, que é de suma importância para o funcionamento do detector, é fornecer o acoplamento óptico entre as fibras e as SiPM. A Figura 5.6 exibe um corte da vista lateral da junção do ROB com o módulo de fibras. O ROB também

Figura 5.4: Luz é produzida no núcleo da fibra por uma partícula passante, e então é aprisionada até que se atinja a extremidade.

é responsável por fornecer resfriamento e estrutura mecânica aos componentes de leitura.

A placa de alumínio que compõe a parede do ROB, indicada na Figura 5.5 por Cooling Plate, atua como dissipadores para os chips de transmissão de dados utilizados na Master Board. Na parte inferior da Figura 5.5 podemos ver a Cold Box, cuja função já não é mais a dissipação de calor mas a conservação da temperatura interna. Esta é ligada ao sistema de resfriamento a fim de manter o conjunto de SiPMs em sua temperatura ótima de operação, que é aproximadamente -40°C. Na Figura 5.6 podemos ver o contato do cano do sistema de resfriamento Cold pipe à parte traseira do módulo do sensor SiPM.

### 5.4 Fotomultiplicadoras de Silício

Fotomultiplicadoras de silício (SiPM) são dispositivos de estado sólido utilizados para detecção de fótons. SiPMs são usadas para detecção da luz proveniente das fibras no detector do SciFi.

SiPMs são formadas por uma matriz de fotodiodos de avalanche em um substrato de silício. Tecnologias atuais permitem a criação de fotodiodos de avalanche com tamanhos

Figura 5.5: Visão explodida de uma *Read-out Box*.

de até  $20\mu$ m, permitindo que uma matriz tenha até 1000 fotodiodos em um milímeto quadrado. Os diodos operam em modo geiger e são ligados em paralelo a saída da SiPM. Cada diodo corresponde a um pixel e o efeito avalanche pode ser disparado por um único fóton. Quando disparado, o diodo satura e gera um nível de corrente fixo e mensurável. Este nível independe do número de fótons incidente no mesmo píxel, pois um único fóton é o suficiente para saturar o diodo. A corrente medida na saída do SiPM será proporcional ao número de diodos saturados, ou seja, ao número de pixels iluminados.

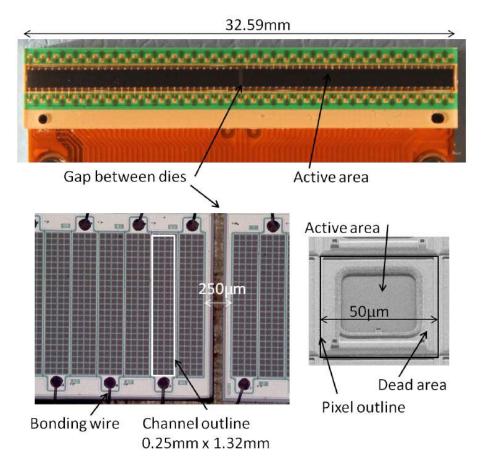

Os modelos de SiPM cotados para uso no SciFi apresentam eficiência de fotodetecção de aproximadamente 40% e ganho de aproximadamente  $2 \times 10^6$ . Um dos modelos possui 128 canais, composto por 2 pastilhas de silício lado a lado, com 64 canais cada. Cada um dos 128 canais são formados por uma matriz de 4 por 24 pixels, totalizando 96 pixels por canal. Os píxels tem dimensões de  $57.5\mu m \times 62.5\mu m$ .

A Figura 5.7 mostra a imagem de uma SiPM, com uma ampliação de seus canais e

Figura 5.6: Corte da vista lateral da junção do módulo de fibras com o módulo ROB.

uma de um unico pixel.

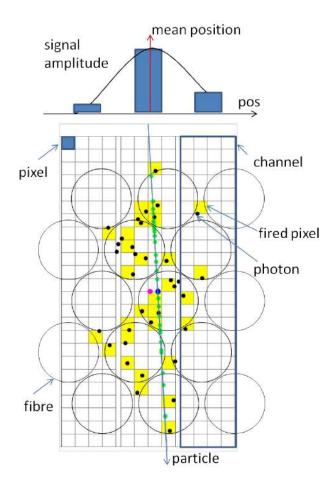

Como podemos ver na Figura 5.8, quando uma partícula atravessa as fibras, é esperado que vários pixels na região das fibras atravessadas sejam iluminados. Embora cada canal tenha  $250\mu m$  de espessura (Figura 5.7), o número de pixels iluminados nos canais adjacentes é uma indicação de quão próxima a partícula estava de qual canal. Comparando a quantidade de carga medida nos canais adjacentes e tirando uma média permite obtermos uma resolução bem inferior aos  $250\mu m$  de largura do canal, obtendo os  $60\mu m$  mencionados anteriormente.

Figura 5.7: Topo: encapsulamento do sensor com 2 pastilhas de silício. Inferior esquerda: ampliação da parte central do sensor, onde se pode ver os canais individuais e o intervalo espacial entre eles. Inferior direita: ampliação de um único pixel.

Figura 5.8: Fótons são gerados por cintilação no interior das fibras, e atingem os pixels marcados em amarelo.

# Capítulo 6

## Eletrônica de Front-End do SciFi

A eletrônica de front-end (FEE) é toda a eletrônica responsável pela interface entre o sinal da SiPM e o módulo de aquisição (contido na back-end). Ela é composta pelos módulos que ficam no local do experimento, juntos ao detector, e é responsável pela leitura do detector e envio dos dados à back-end. Adicionalmente a FEE também é responsável pelo controle e monitoramento do sistema do detector, recebendo comandos de controle e enviando relatórios solicitados sobre os status dos componentes. Como visto anteriormenete, a front-end ficará contida nos ROBs, que se encontrarão anexados na extremidade de cada módulo de fibras.

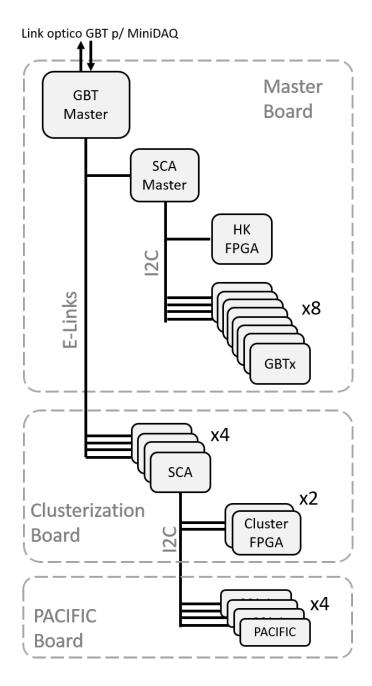

A eletrônica do SciFi é composta por 3 tipos de módulos que exercem funções de leitura, processamento e envio:

- Pacific Board: é o módulo responsável pela leitura, amplificação e digitalização dos dados provenientes das SiPM.

- Clusterization Board: é o módulo responsável pelo agrupamento dos dados em clusters para envio à back-end.

- Master Board: é o módulo que controla os demais, provê alimentação, clock, e é responsável pelo envio dos dados.

A front-end do SciFi utiliza os componentes do Projeto "Giga-Bit Transceiver" (GBT) [16]. Na front-end se encontram os chips GBTx e GBT SCA, ambos explicados na Seção 4.1. No SciFi, o GBT SCA é utilizado para comunicação com todos os dispositivos I2C da front-end.

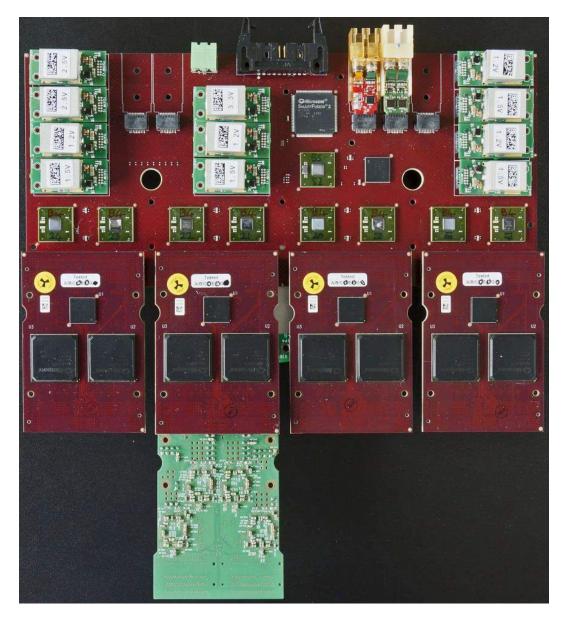

Figura 6.1: Imagem com protótipos das placas da front-end. Na parte superior se vê o protótipo da Master Board, com 11 conversores DC-DC plugados nela, e 2 módulos de transmissão ópticos. Na parte central, conectadas abaixo da Master Board se encontram 4 protótipos da Clusterization Board. Na parte inferior da imagem se vê um protótipo da Pacific Board conectado à segunda Clusterization Board.

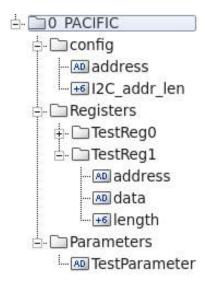

## 6.1 Pacific Board e o Chip PACIFIC

A Pacific Board é o módulo que faz a leitura das SiPM. Ela contém 4 chips "low-Power ASIC for the sCIntillating FIbres traCker" (PACIFIC) [17]. PACIFIC é um circuito integrado de aplicação específica (ASIC) de sinal misto, desenvolvido com tecnologia 130nm CMOS, com o objetivo de ser o chip de leitura do SciFi. O PACIFIC possui 64 canais de entrada, consumindo menos de 8mW por canal e com taxa de amostragem de 40MHz. O PACIFIC é também controlado via I2C. Ele é responsável por amplificar e digitalizar o sinal das SiPM, convertendo estes para um valor digital de 2 bits.

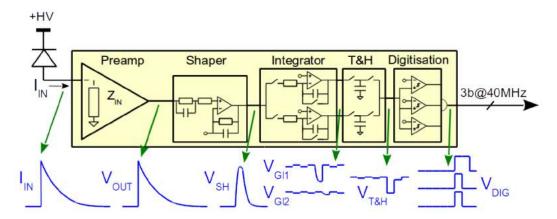

Na Figura 6.2 podemos ver as etapas de processamento do sinal no chip PACIFIC.

Figura 6.2: Cadeia de processamento de sinal por canal no chip PACIFIC.

Os itens da Figura 6.2 são explicados a seguir:

- O componente Preamp é um amplificador de transimpedância que converte o sinal de corrente proveniente da SiPM em um sinal idêntico com um ganho configurável aplicado. O ganho pode ser escolhido entre 4 opções (0,5x; 1x; 1,5x e 2x) através da interface I2C.

- O Shaper é um bloco de processamento de sinal que efetua cancelamento de polos e zeros. A finalidade é remover a cauda do sinal do SiPM e cancelar "overshoots" e "undershoots". Os valores para os polos e zeros, assim como no Preamp, também são configuráveis através de I2C.

- O *Integrator* é um bloco integrador, que utiliza a arquitetura clássica de integrador compreendendo um amplificador operacional com um resistor na entrada do sinal para a entrada negativa e um capacitor para a saída. Este bloco, no entanto, utiliza dois integradores que se alternam em função de clock, de modo a evitar tempo morto. Enquanto um está ativo, o outro está descarregando e vice-versa.

- O bloco T&H é um "Track and Hold", um circuito que amostra o valor do sinal e o mantém por um tempo, para que o sinal fique estável durante o tempo de conversão do conversor analógico-digital.

- o bloco "Digitisation" é o responsável pela digitalização do sinal. A saída do digitalizador é um sinal binário de 2 bits formado a partir de 3 comparadores cujos sinais de thresholds podem ser configurados pela interface I2C.

A Pacific Board contém 4 chips PACIFIC, permitindo portanto a leitura de 2 SiPM de 128 canais por placa PACIFIC. Cada Master Board suporta até 4 Pacific Boards, e por isso uma Master Board recebe o sinal de 8 SiPMs e consequentemente cada ROB lê 16 SiPMs.

Após digitalizado o sinal, este é enviado para a Clusterization Board.

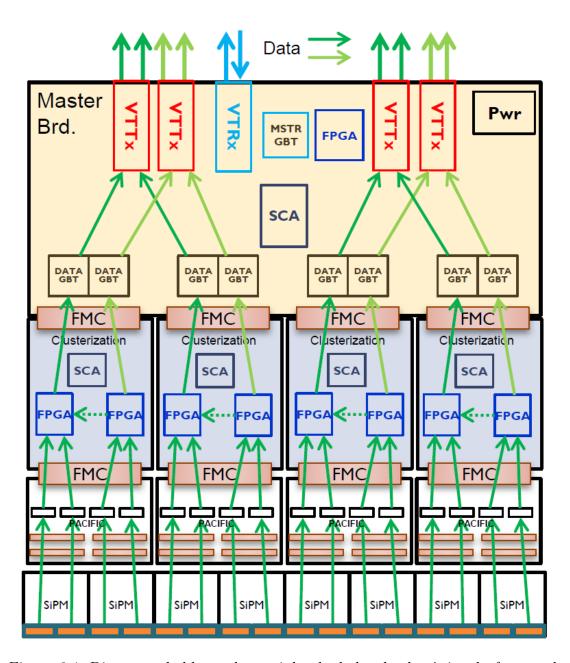

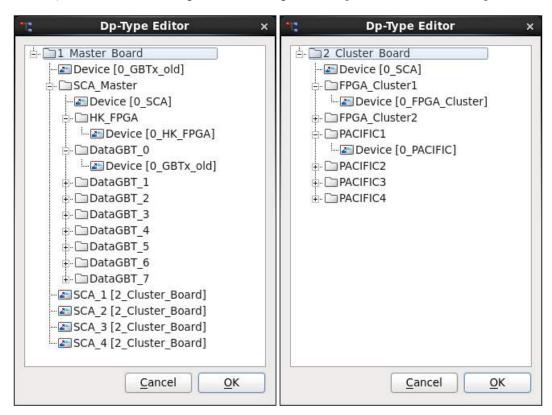

#### 6.2 Clusterization Board

A Clusterization Board é o módulo responsável pelo preparo dos dados vindos do PACIFIC para envio à back-end. Ela exerce duas funções principais: a formação de clusters e a supressão de zeros. A Clusterization Board possui um GBT SCA e dois FPGAs Igloo2 da Microsemi que são chamados "Clusterization FPGAs". O papel do GBT SCA é a configuração dos FPGAs e dos chips da Pacific Board. Já os FPGAs são os responsáveis pelo tratamento dos dados e pelos algoritmos de supressão de zeros e clusterização. A cada Clusterization Board será conectada uma Pacific Board, e cada Master Board recebe 4 Clusterization Boards.

Os dados lidos do detector não são enviados de forma crua para a back-end, mesmo porque o volume de dados é grande demais para que fossem enviada a leitura de todos os canais de todas as SiPM. A maioria dos canais lê zero em grande parte dos eventos, uma vez que o número de partículas produzidas nas colisões é relativamente pequeno comparado ao número de canais que o detector possui. Este fato permite a utilização de uma técnica para lidar com o excesso de dados, que é a supressão dos zeros. Esta suprime os canais que lêem zero antes de enviar os dados. Assim salva-se banda que do contrário estaria sendo desperdiçada enviando zeros atrás de zeros. A supressão de zeros, por outro lado, pode aumentar o volume de dados enviados uma vez que quando se suprime alguns canais, é necessário enviar também a informação de quais canais foram ou não suprimidos. Se a

informação de quais canais são referentes aos dados enviados ocupar mais espaço do que o que se economiza com a supressão dos canais lidos zero, deixa de valer a pena a supressão de zeros. Os FPGAs de clusterização também são configuráveis via I2C e esta função pode ser habilitada ou desabilitada durante tempo de execução.

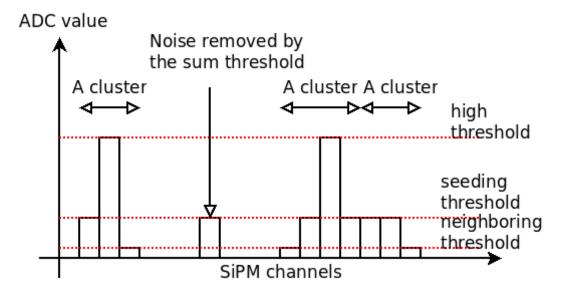

Outra importante função do FPGA de Clusterização é o algoritmo de clusterização. Este processa os dados dos canais do detector a fim de julgar o que será considerado uma partícula ou o que será considerado ruído. Na Figura 5.8 pudemos ver um exemplo de leitura nos canais da SiPM. Observe que uma partícula pode não atingir um único canal, mas ao invés, tende a iluminar mais pixels dos canais por onde sua trajetória mais se estendeu.

O FPGA de clusterização recebe os dados no formato de 2 bits por canal. Estes 2 bits significam qual o valor lido pelo PACIFIC em função dos thresholds. São 3 thresholds e por isto 4 possibilidades (2 bits). O algoritmo analisa se a carga total depositada em dado canal e nos adjacentes são o suficiente para considerar que a leitura se trata de uma partícula. Ou ainda, se o valor corresponde a duas ou mais partículas que acertaram canais adjacentes.

Na Figura 6.3 podemos ver exemplos de clusters.

Figura 6.3: Leitura dos canais da SiPM com indicação do que seriam considerados clusters pelo algoritmo de clusterização.

À esquerda da Figura 6.3 houve uma leitura que foi considerado um *cluster*. Ao centro há uma leitura que o algoritmo não considerou como *cluster* pois o somatório do

valor do canal e adjacentes não somou o suficiente para representar uma partícula. Já a leitura da direita, o algoritmo interpretou como dois clusters. Primeiro porque o número de canais atingidos foi mais do que 4, e também porque a energia total seria o suficiente para considerar como dois.

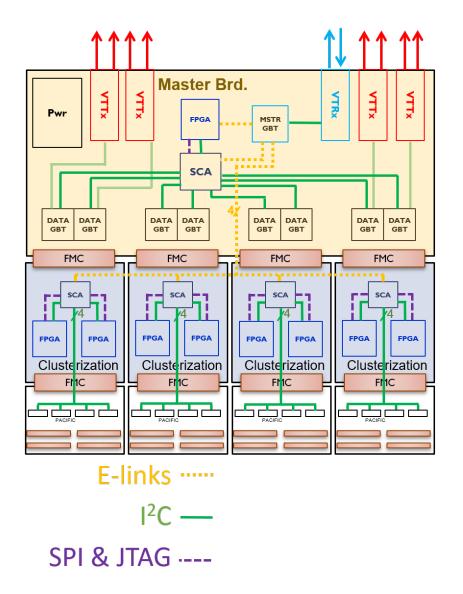

#### 6.3 Master Board

A Master Board é o módulo principal que compõe a eletrônica de *front-end*. Ela é responsável por gerenciar os demais componentes da *front-end*, fornecer alimentação, gerar e distribuir sinais de controle, clock, e enviar os dados provenientes da clusterização.

Os principais componentes da Master Board são listados a seguir, e podem ser vistos na Figura 6.4:

- **GBTx Master**: é o chip responsável por toda a comunicação com a *front-end*. É um GBTx configurado como mestre. Ele é a porta de entrada, que distribui todos os comandos enviados à *front-end* para os GBT SCAs através dos e-links. O GBTx Master está marcado como "MSTR GBT" na Figura 6.4.

- SCA Master: é o GBT SCA responsável pelo controle dos demais componentes da Master Board. Note que ele é chamado Master apenas por estar na Master Board, e não por ter algum tipo de configuração mestre-escravo. Este GBT SCA recebe comandos do GBTx Master através de um e-link e através de suas portas I2C é feito a configuração dos 8 GBTx de dados e do HouseKeeping FPGA.

- GBTx de dados: são os GBTx responsáveis pelo envio dos dados provenientes das Clusterization Boards. A saída de cada GBTx de dados é ligada a um canal dos transmissores ópticos VTTx.

- HouseKeeping FPGA: abreviado para HK FPGA, é o dispositivo responsável pelo gerenciamento local dos componentes da Master Board. Ele administra os sinais de reset dos demais componentes, status da alimentação e dos conversores DC, e controla a sequência de inicialização dos componentes. Trata-se de um FPGA Microsemi M2GL005-vf256, com configuração baseada em memória FLASH, o que contribui para ser resistente a radiação.

- Módulos de transmissão óptica: a Master Board utiliza módulos Versatile Link VTTx e VTRx. Versatile Link é um projeto de transmissores ópticos resistentes a radiação, para serem utilizados no upgrade do LHC. O projeto compreende alguns tipos de transmissores. Os utilizados na Master Board são 4 "Versatile Transmitter-Transmitter" (VTTx) e 1 "Versatile Transmitter-Receiver" (VTRx). O VTTx dispõe de 2 transmissores ópticos, cada um transmite os dados de 2 GBTx. O VTRx possui um transmissor e um receptor, sendo este o utilizado pelo GBTx Master, o único componente do módulo que possui um link bidirecional.

- Fontes de alimentação: a Master Board utiliza módulos conversores DC-DC para alimentar seus componentes e as placas anexadas. Ela utiliza módulos de 1,2V, 1,5V, 2,5V e 3,3V. Os módulos são projeto do CERN para um conversor DC-DC tolerante a radiação e pequeno em massa. Mais sobre os conversores pode ser encontrado em [18].

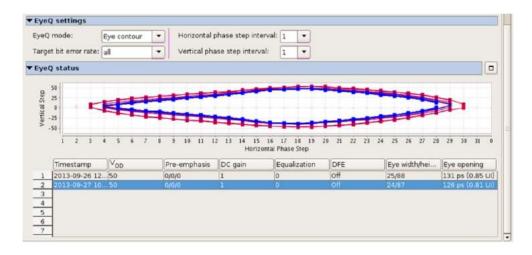

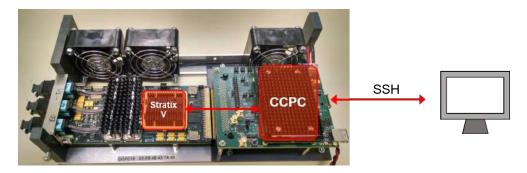

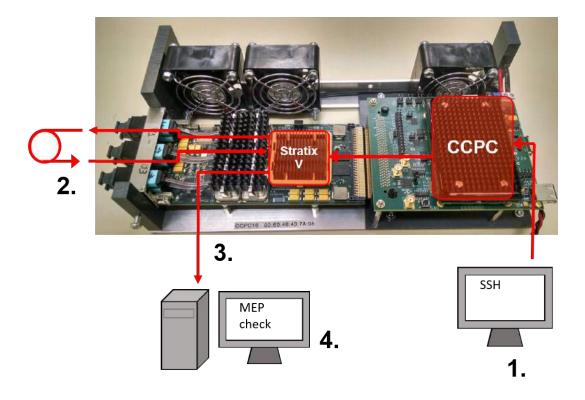

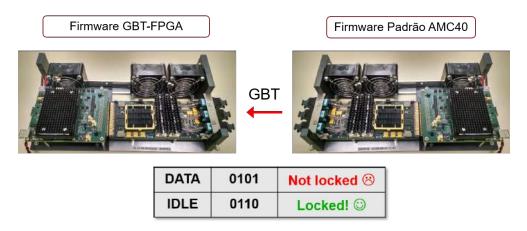

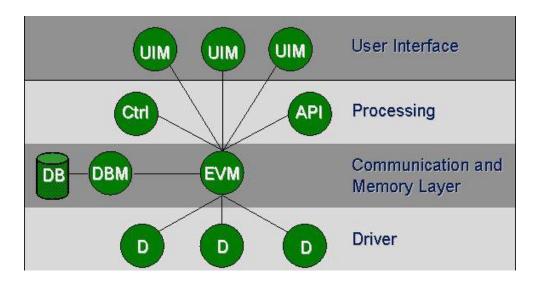

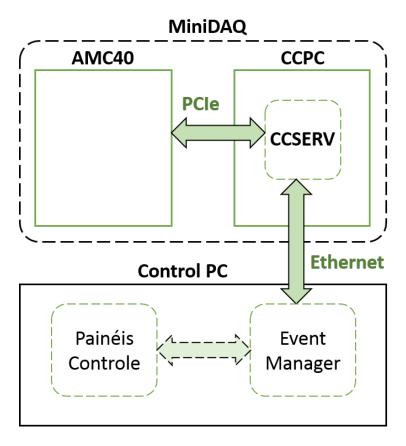

#### 6.4 Caminho de Dados Alternativo